INSTITUTO DE ENGENHARIA NUCLEAR

PÂMELA IARA NOLASCO TEIXEIRA

MODELAGEM DE FUNÇÕES CRÍTICAS DE REATORES NUCLEARES

UTILIZANDO FIELD PROGRAMMABLE GATE ARRAY

Rio de Janeiro

2016

INSTITUTO DE ENGENHARIA NUCLEAR

PÂMELA IARA NOLASCO TEIXEIRA

**MODELAGEM DE FUNÇÕES CRÍTICAS DE REATORES

NUCLEARES UTILIZANDO FIELD PROGRAMMABLE GATE ARRAY**

Dissertação apresentada ao Programa de Pós-Graduação em Ciência e Tecnologia Nucleares do Instituto de Engenharia Nuclear da Comissão Nacional de Energia Nuclear como parte dos requisitos necessários para a obtenção do grau de Mestre em Ciências em Engenharia Nuclear – Acadêmico em Engenharia de Reatores.

Orientadores: Paulo Victor Rodrigues de Carvalho

Mauro Vitor de Oliveira

Rio de Janeiro

2016

TEIX Teixeira, Pâmela Iara Nolasco

Modelagem de funções críticas de reatores nucleares utilizando

Field Programmable Gate Array/Pâmela Iara Nolasco Teixeira. –

Rio de Janeiro: CNEN/IEN, 2016

x, 119f. : il.,; 31 cm

Orientadores: Paulo Victor Rodrigues de Carvalho

Mauro Vitor de Oliveira

Dissertação (mestrado em Ciência e Tecnologia Nucleares

Métodos Computacionais Aplicados) – Instituto de Engenharia

Nuclear, PPGIEN, 2016.

1. Segurança. 2. Função Crítica de segurança. 3. Proteção.

## AGRADECIMENTOS

Agradeço primeiramente a Olorum (Deus), aos sagrados orixás que me deram caminho, força e perseverança para que eu pudesse vencer mais uma etapa em minha evolução.

Agradeço a bolsa cedida pela CENEN.

Aos meus pais Maria Auxiliadora e Adilson, minha irmã Ana Carolina, por estarem sempre ao meu lado em todos os momentos.

Ao meu marido Eduardo e minha filha Bruna, pela compreensão e amor nos dias difíceis.

Aos meus familiares e amigos que sempre me apoiaram e incentivaram ao longo do trabalho.

Ao meu amigo irmão Roque Hudson, companheiro de todas as horas.

Ao amigo Rogério Clynton Ribeiro, que muito me auxiliou nos momentos decisivos.

Ao Dr. Paulo Victor Rodrigues de Carvalho pela orientação.

Ao Dr. Mauro Vitor de Oliveira pela orientação.

Ao M. Sc Marcos Santana Faria.

Aos amigos que o mestrado me trouxe.

“Se não puder voar, corra; se não puder correr, ande. Se não puder andar, rasteje, mas continue em frente de qualquer jeito.”

Martin Luther King

## RESUMO

O presente trabalho propõe o desenvolvimento de um método para modelagem de funções críticas de segurança de um reator nuclear utilizando FPGA implementadas por VHDL, que é uma forma de se descrever, através de um programa, o comportamento de um circuito ou componente digital. Foram implementadas duas funções críticas de segurança, FCS de Resfriamento do Núcleo, responsável por resfriar o núcleo do reator nas paradas da usina e também na hipótese de acidentes com perda de refrigerante e FCS Transferência de Calor, responsável por refrigerar o núcleo do reator na hipótese de um acidente com perda de refrigerante. Nesta Dissertação foi escolhido a utilização do FPGA, pois, devido aos efeitos do envelhecimento, problemas de obsolescência, degradação ambiental e falhas mecânicas, as usinas nucleares precisam substituir seus sistemas mais antigos por sistemas baseados em tecnologias digitais. Os resultados obtidos utilizando um sistema descrito em linguagem de hardware pode ser implementado em um dispositivo programável, tendo a grande vantagem da alteração do código a qualquer momento.

Palavras-chave: Segurança; Função Crítica de Segurança; Proteção

## **ABSTRACT**

This paper proposes the development of a method using FPGA for critical security functions of a nuclear reactor. It was implemented two critical safety functions in VHDL, which is a way to describe, through a program, the behavior of a circuit or digital component. Which is one way to describe, through a program, the behavior of a digital circuit or component. They were implemented two critical security functions, FCS Core Cooling, responsible for cooling the reactor core in the charts of the plant and also in the event of accidents involving loss of coolant and FCS Heat Transfer, responsible for cooling the reactor core in the event an accident with loss of coolant. In this Dissertation was the use of FPGA chosen because, due to the effects of aging, obsolescence issues, environmental degradation and mechanical failures, nuclear power plants need to replace their older systems by systems based on results digitais. The technologies obtained using a system described hardware language can be implemented in a programmable device, having the advantage of changing the code at any time

**Keywords:**Safety;Critical Safety Functions; Protection

## LISTA DE FIGURAS

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| Figura 1– Representação da usina angra I .....                                | 23 |

| Figura 2– Representação da vareta e elemento combustível .....                | 28 |

| Figura 3– Representação do elemento combustível .....                         | 28 |

| Figura 4– Representação da contenção .....                                    | 29 |

| Figura 5– Representação do edifício do reator .....                           | 30 |

| Figura 6– Interação do sistema de SPDS e FCS e operador .....                 | 37 |

| Figura 7– Árvore de estados genérica .....                                    | 39 |

| Figura 8 – Arquitetura genérica de uma FPGA .....                             | 45 |

| Figura 9– Configuração básica de um CLB .....                                 | 46 |

| Figura 10– Diagrama de bloco de um módulo lógico. ....                        | 47 |

| Figura 11– Modelo de um núcleo rígido embutido em uma FPGA.....               | 48 |

| Figura 12– Arquitetura básica de roteamento de um FPGA .....                  | 51 |

| Figura 13– Mercado de FPGA no ano de 2005 .....                               | 52 |

| Figura 14 – Uma tela de operação do simulador do LABIHS .....                 | 60 |

| Figura 15– Visão geral da sala de controle do simulador LABIHS.....           | 61 |

| Figura 16– Tela de operação principal do simulador LABIHS .....               | 62 |

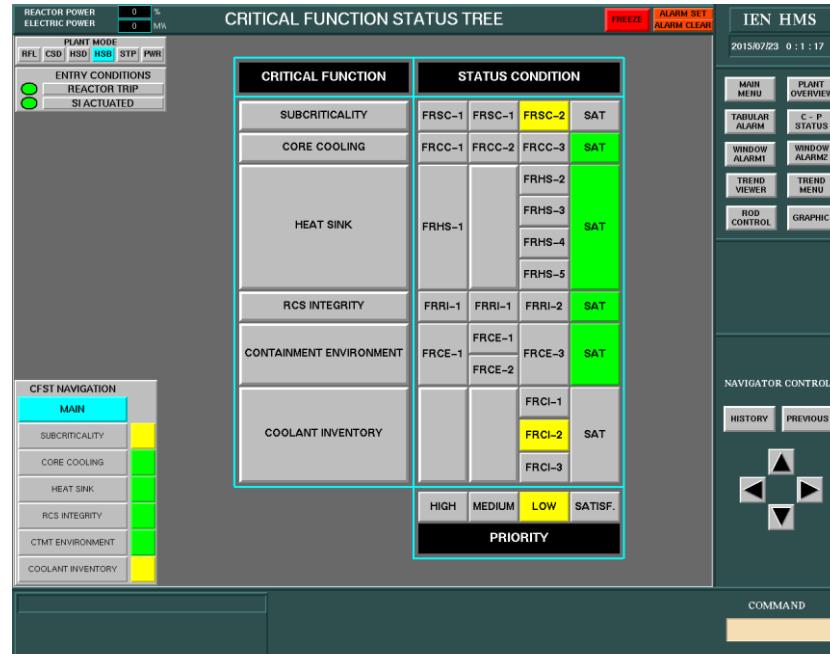

| Figura 17– Tela principal das FCS do simulador LABIHS .....                   | 63 |

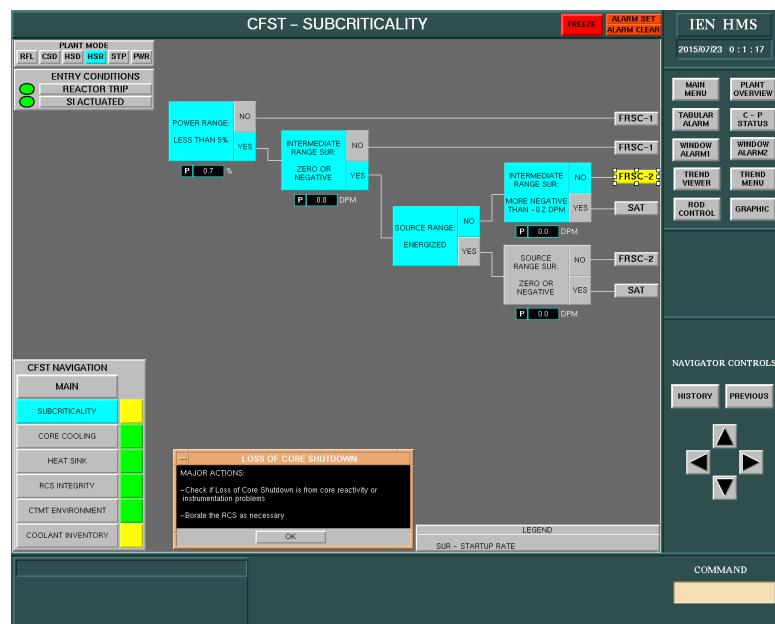

| Figura 18 – Tela da FCS subcriticalidade do LABIHS.....                       | 63 |

| Figura 19– Metodologia de Projeto de SD com o Quartus <sup>(R)</sup> II ..... | 64 |

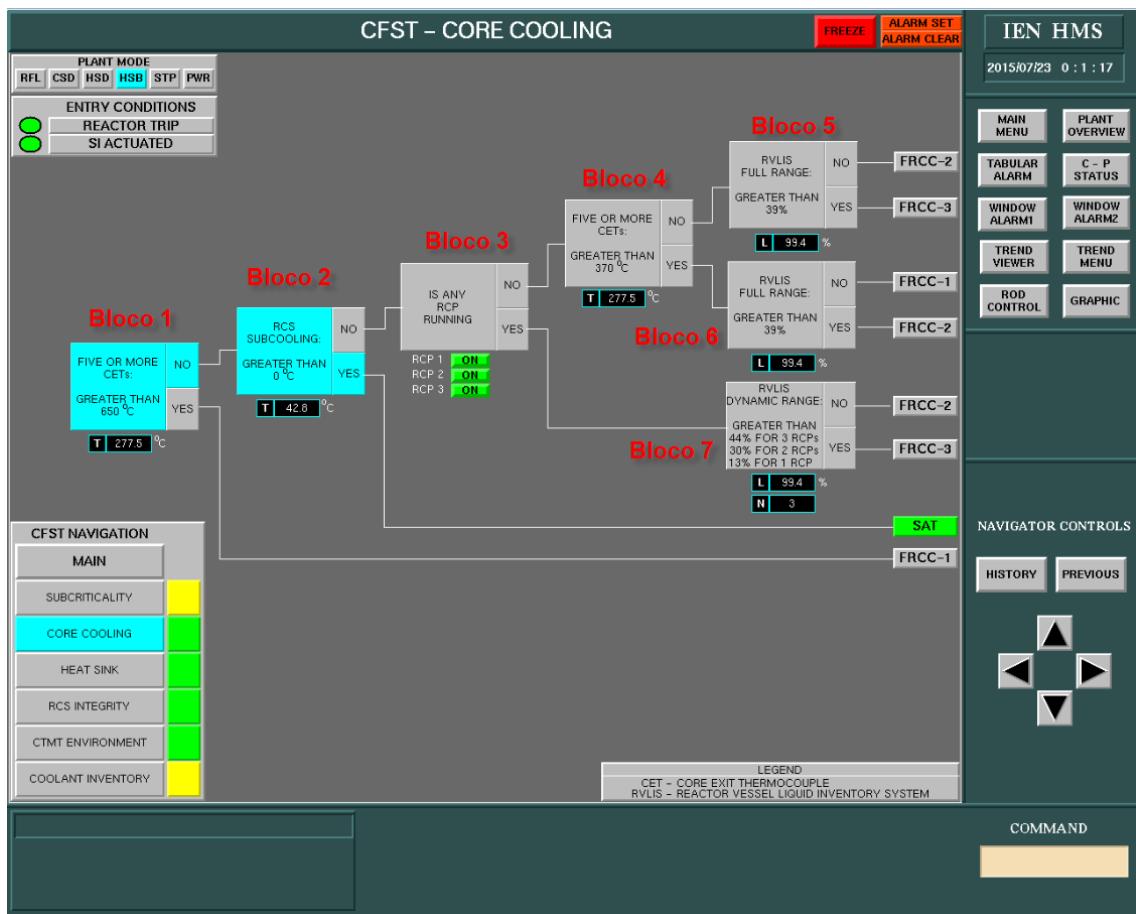

| Figura 20– Numeração dos blocos da FCS Resfriamento do Núcleo.....            | 68 |

|                                                                        |    |

|------------------------------------------------------------------------|----|

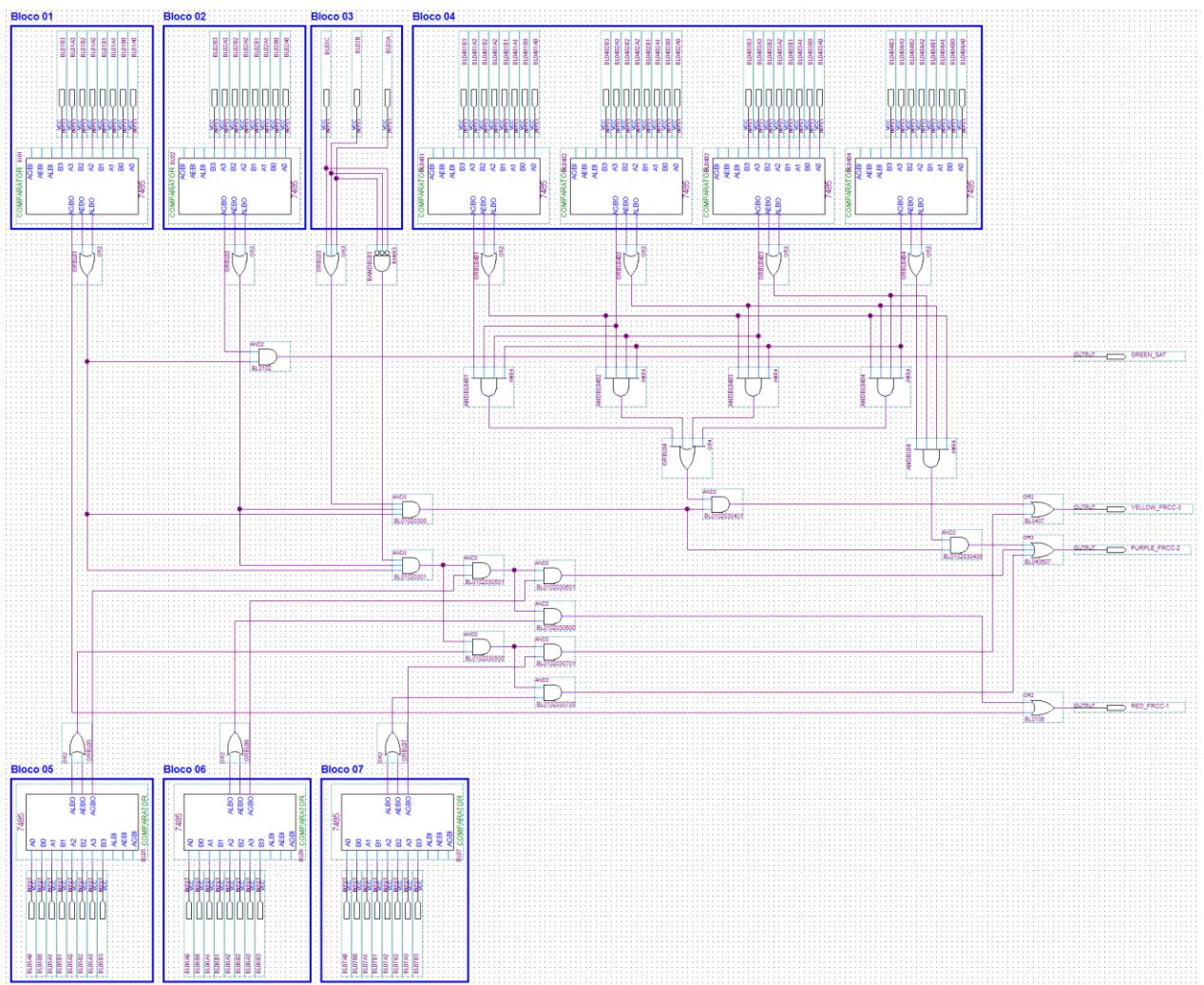

| Figura 21– Esquemático da FCS referente ao Resfriamento do núcleo..... | 71 |

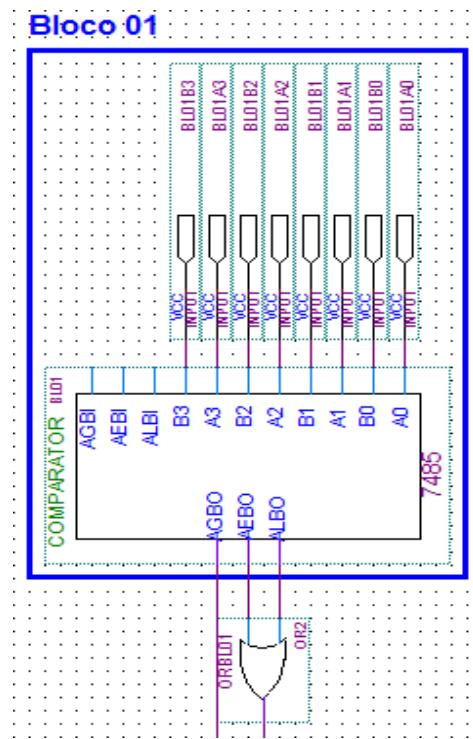

| Figura 22– Bloco 1 .....                                               | 74 |

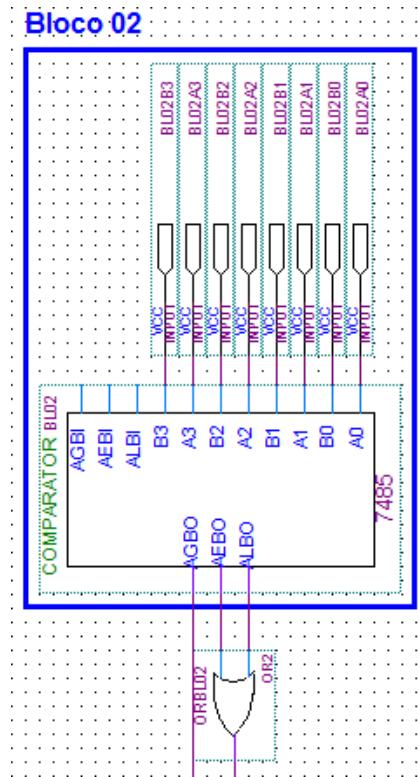

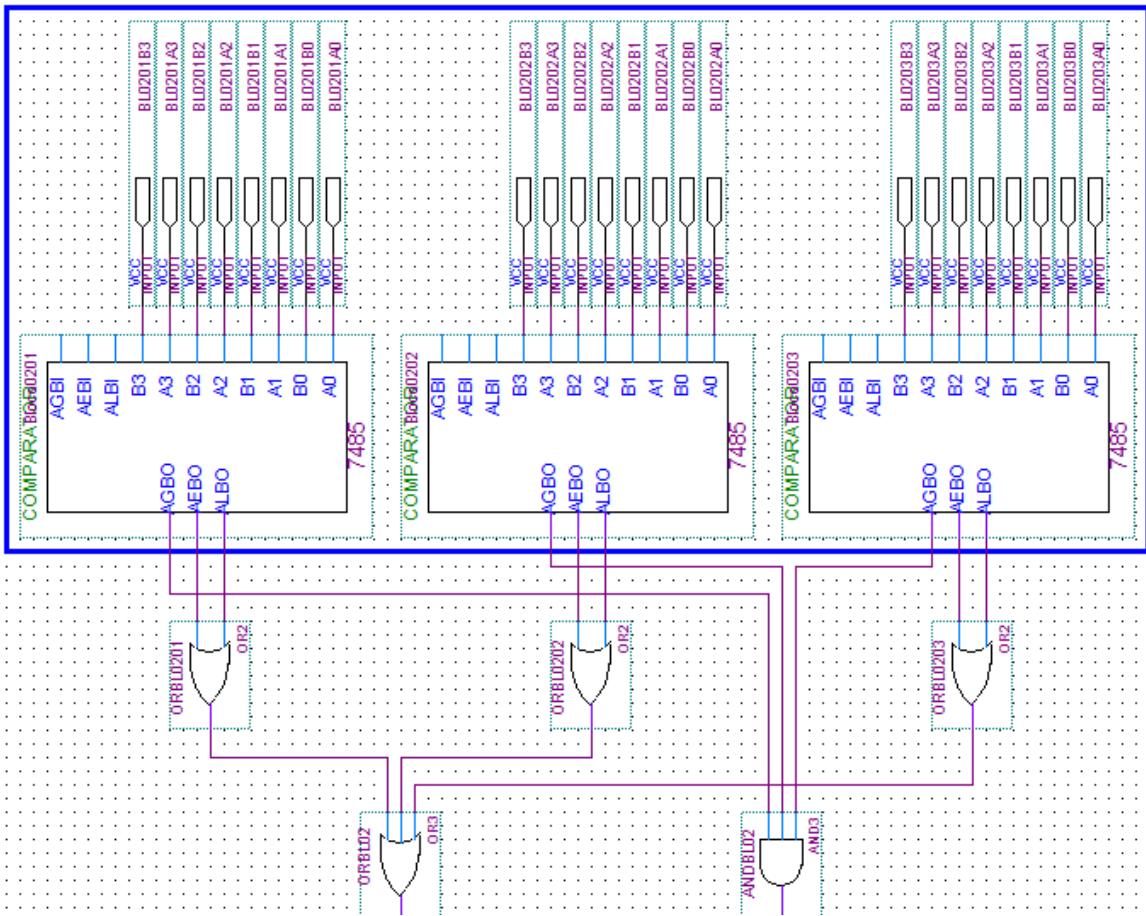

| Figura 23– Bloco 2 .....                                               | 75 |

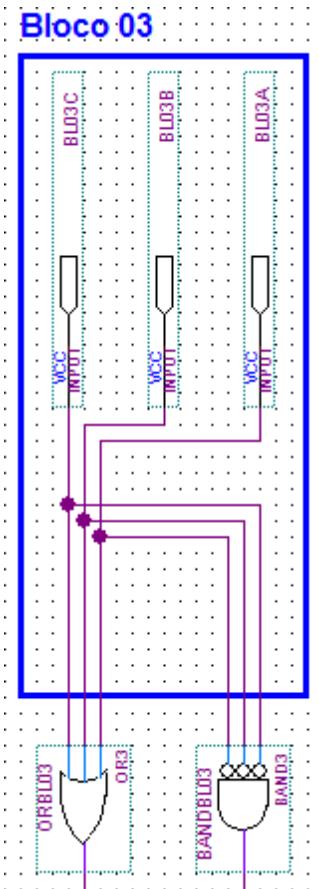

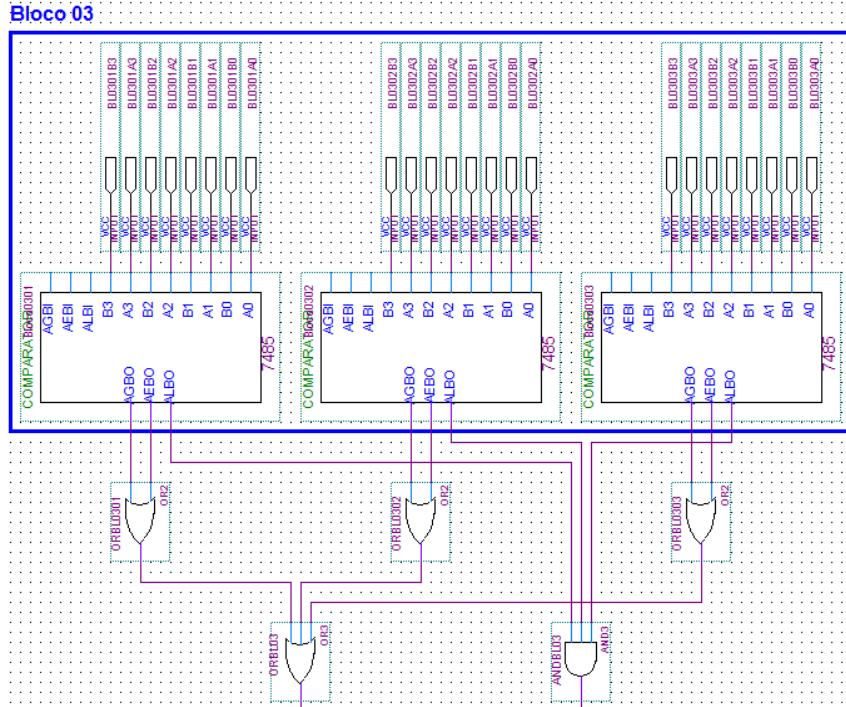

| Figura 24 – Bloco 3.....                                               | 76 |

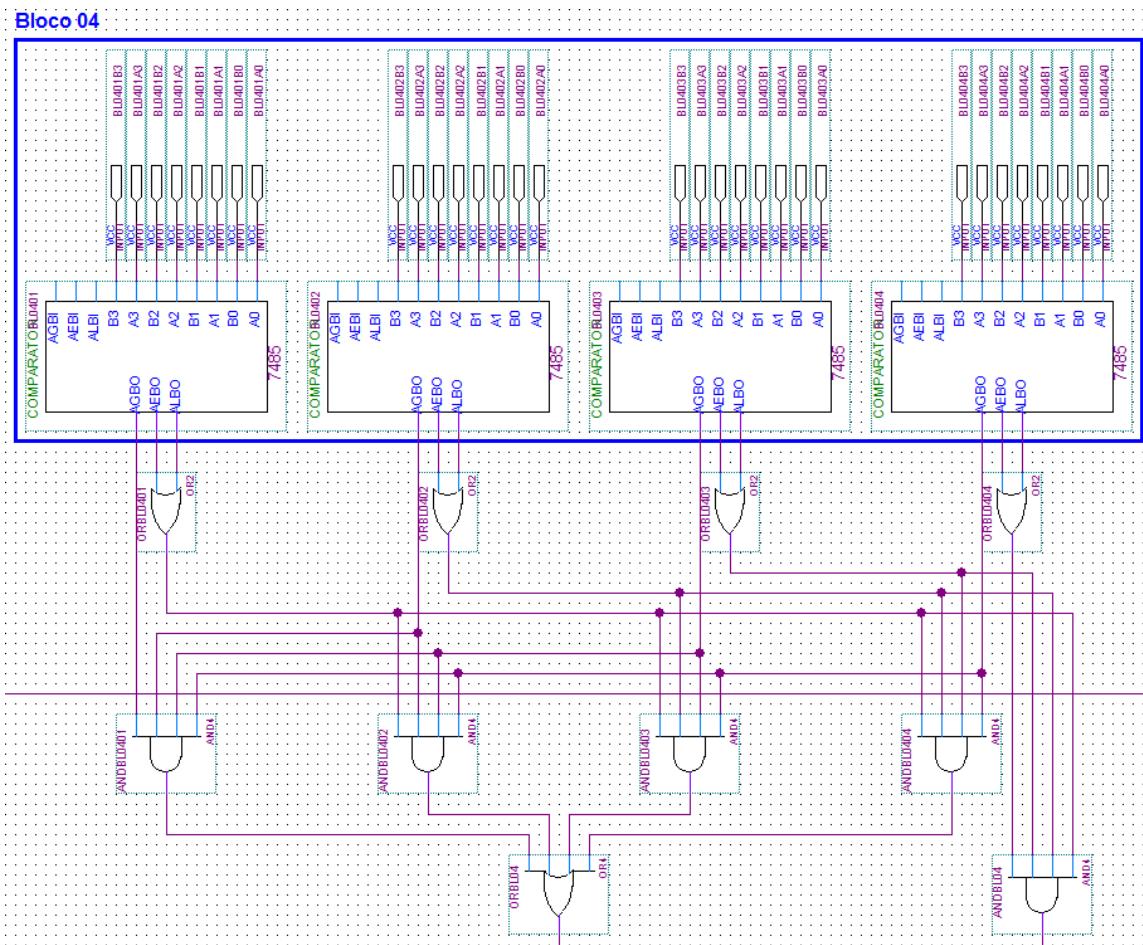

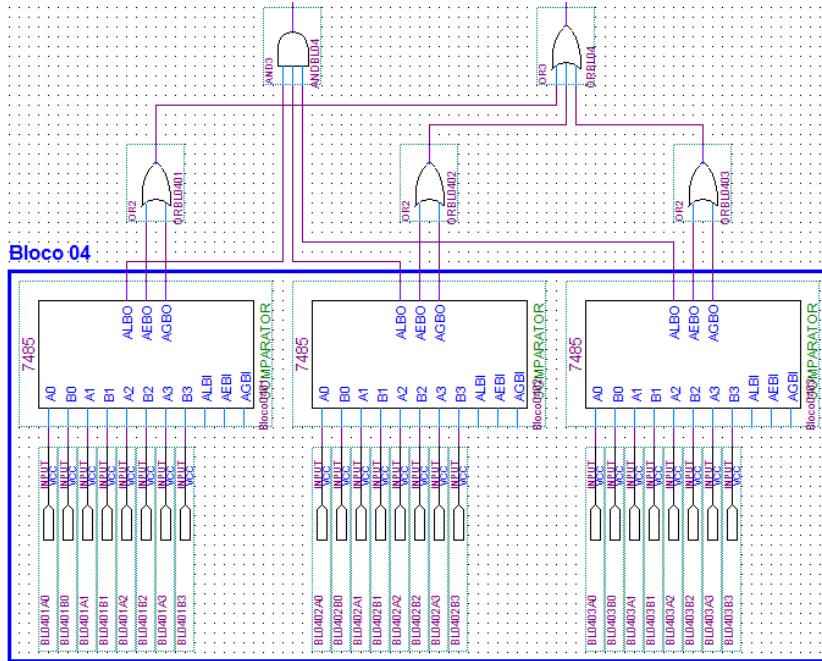

| Figura 25– Bloco 4 .....                                               | 77 |

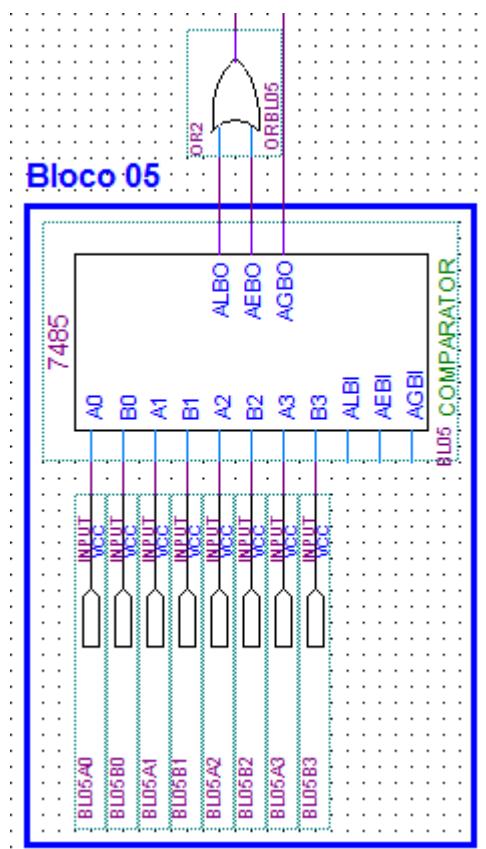

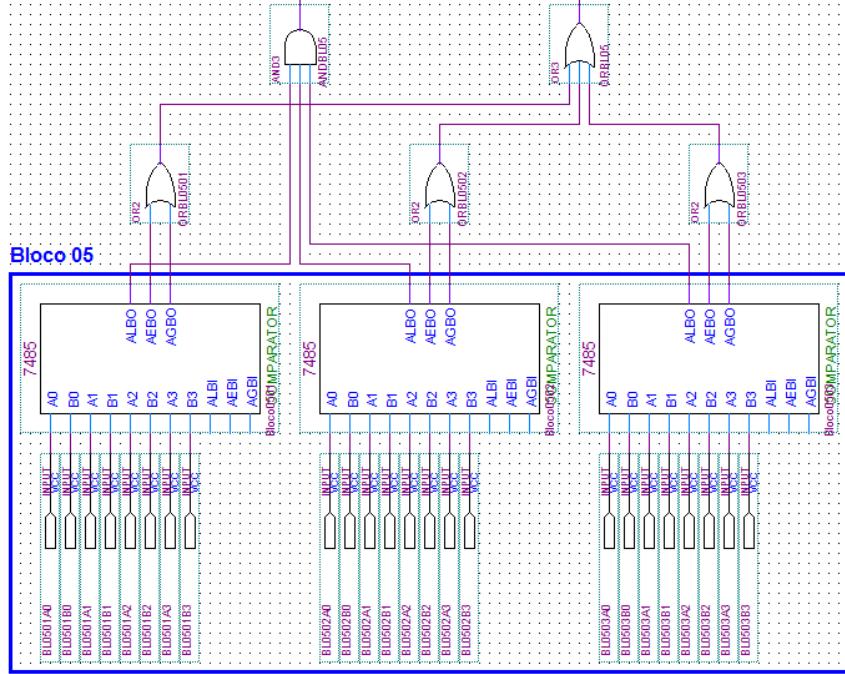

| Figura 26– Bloco 5 .....                                               | 78 |

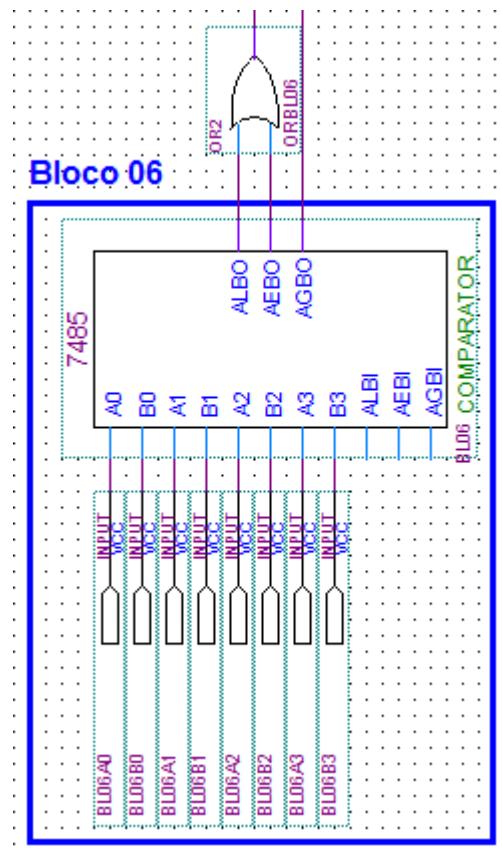

| Figura 27 – Bloco 6.....                                               | 79 |

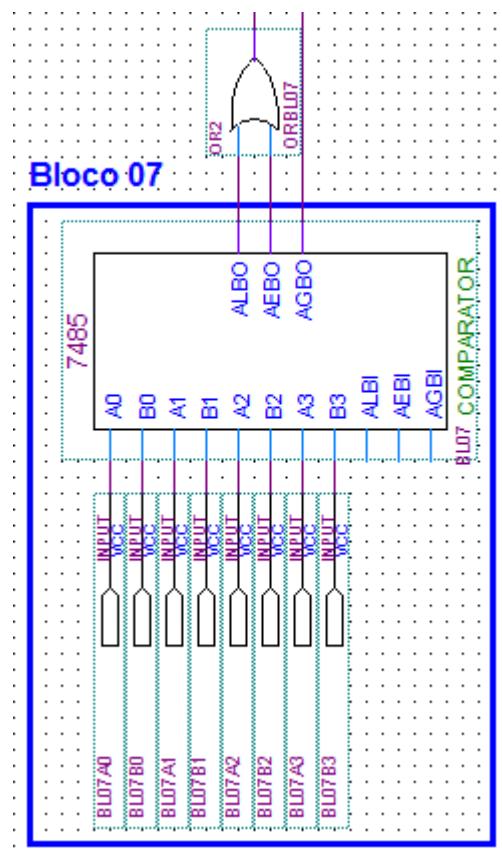

| Figura 28– Bloco 7 .....                                               | 80 |

| Figura 29– Agrupamento das Entradas .....                              | 81 |

| Figura 30 – Agrupamento dos Comparadores do bloco 1.....               | 82 |

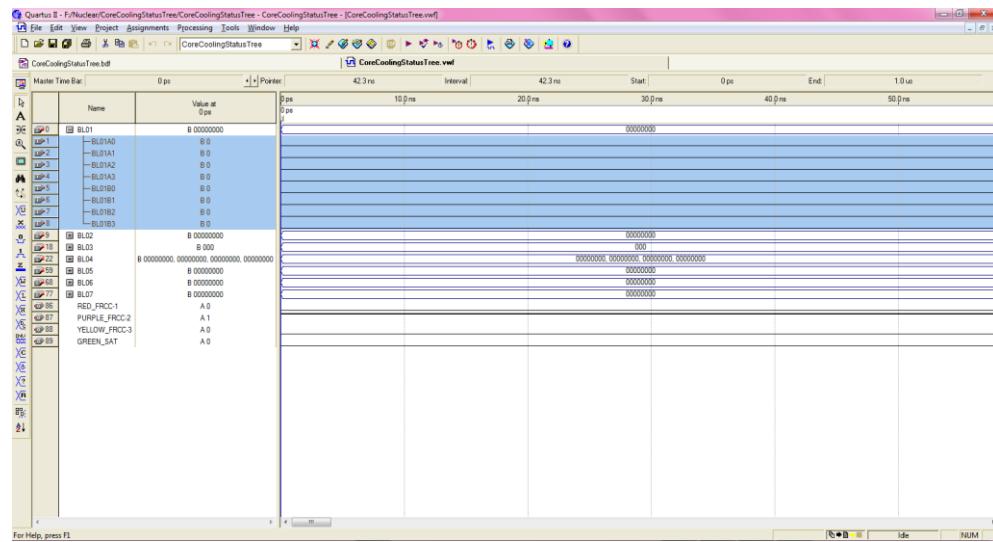

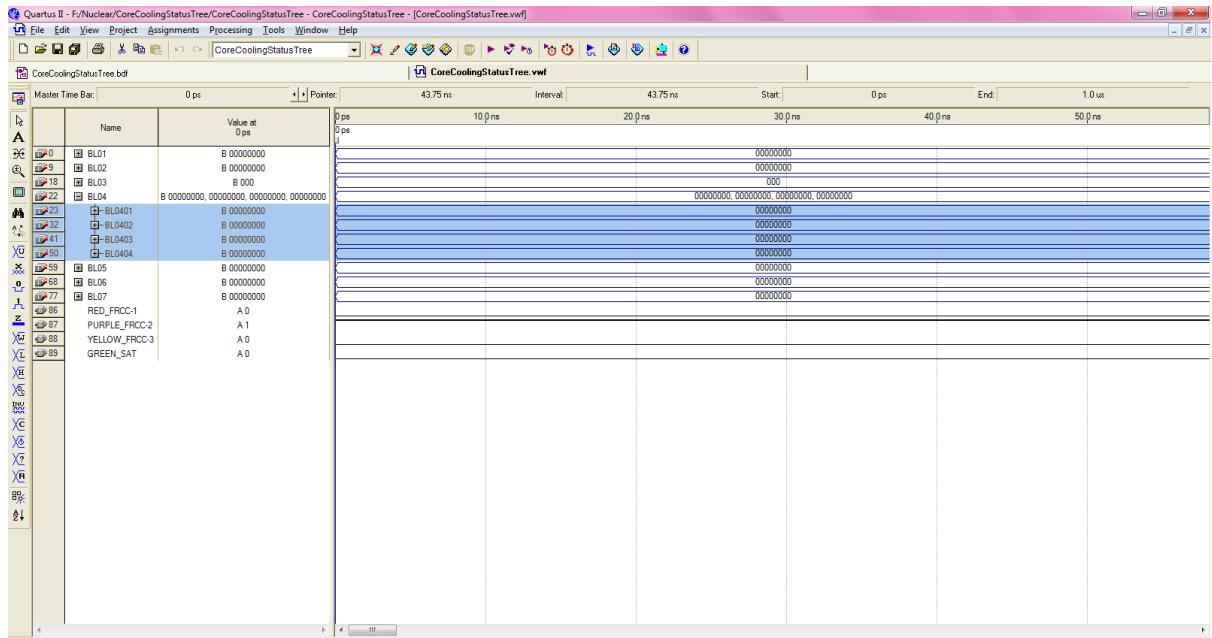

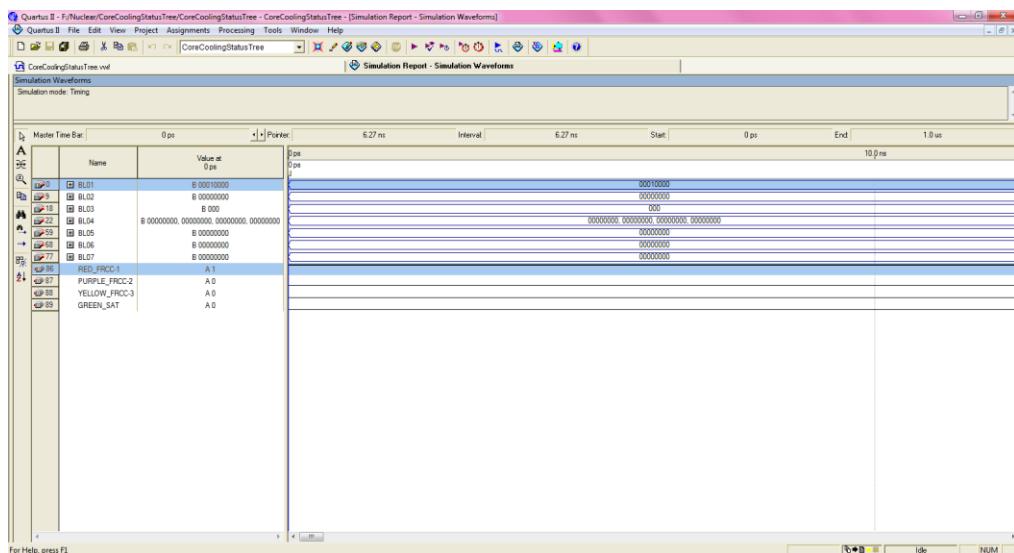

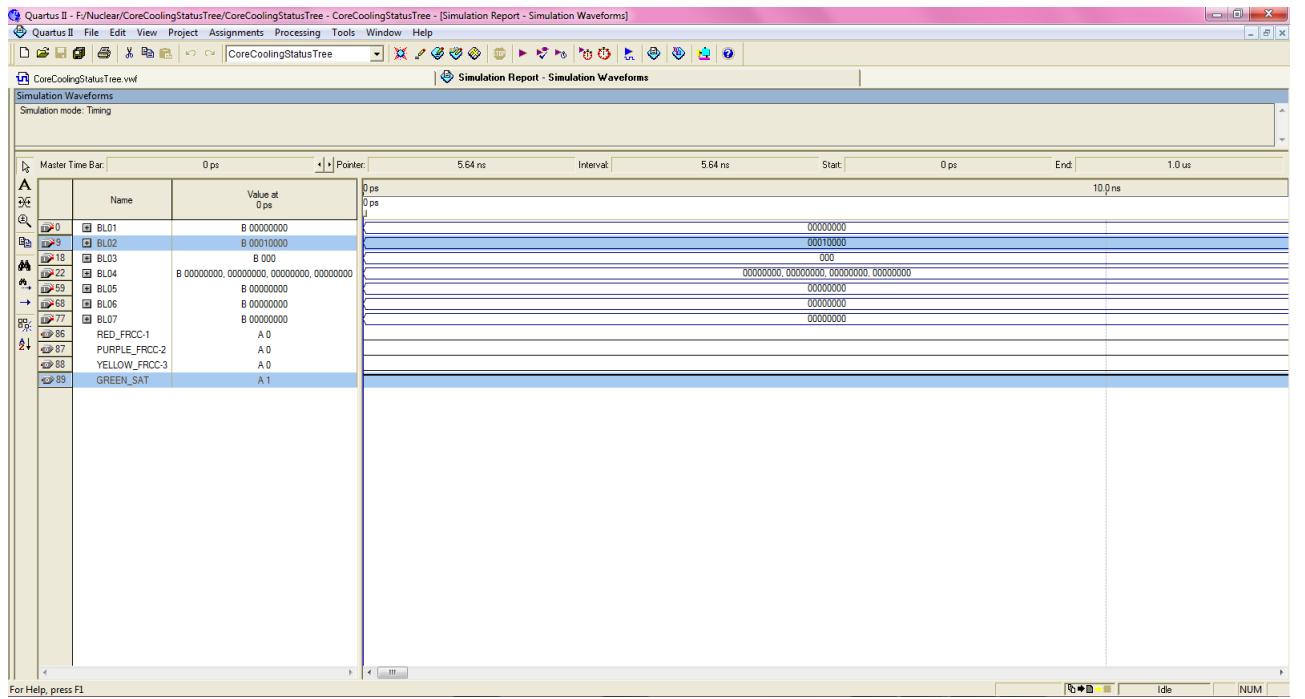

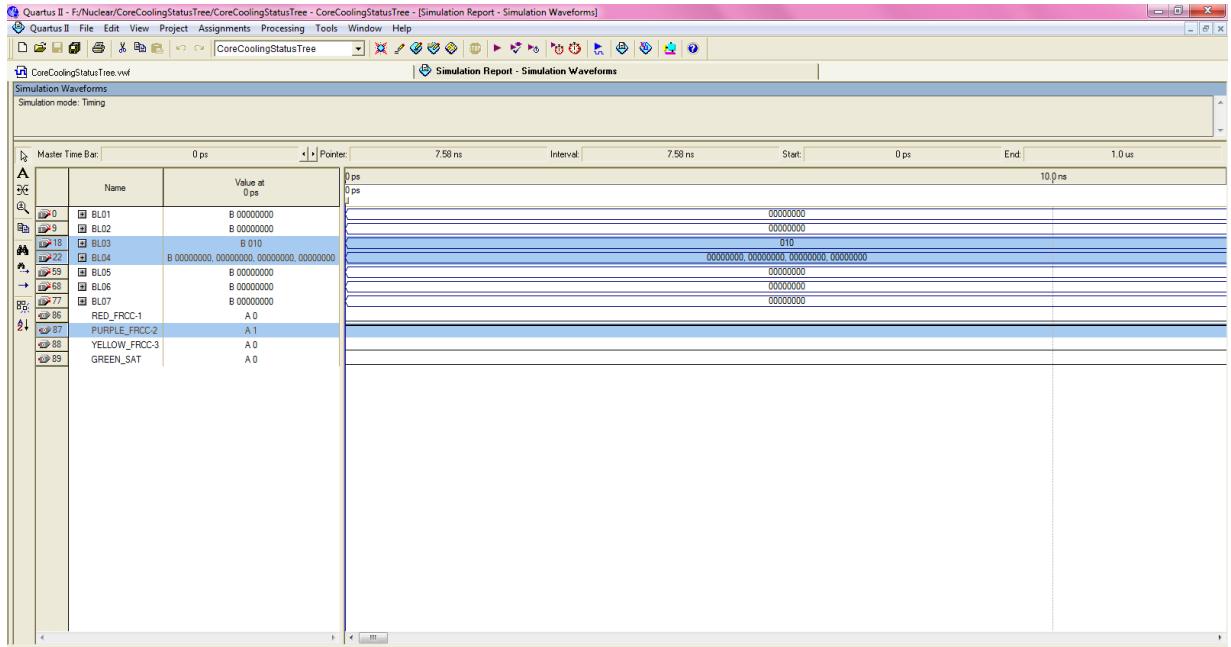

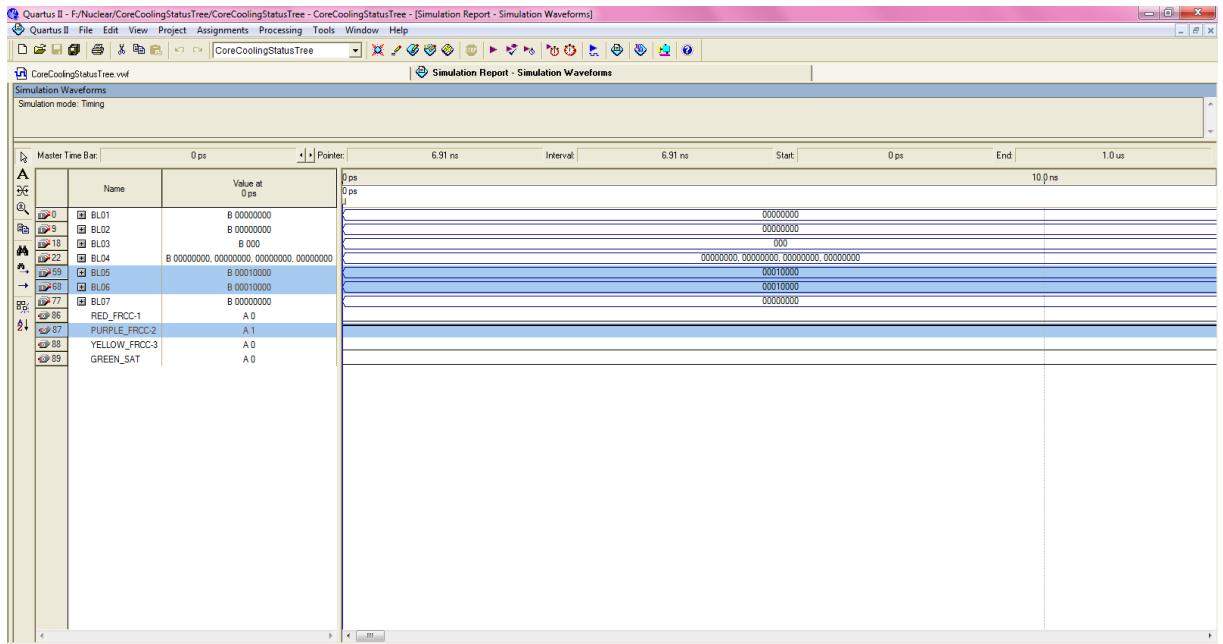

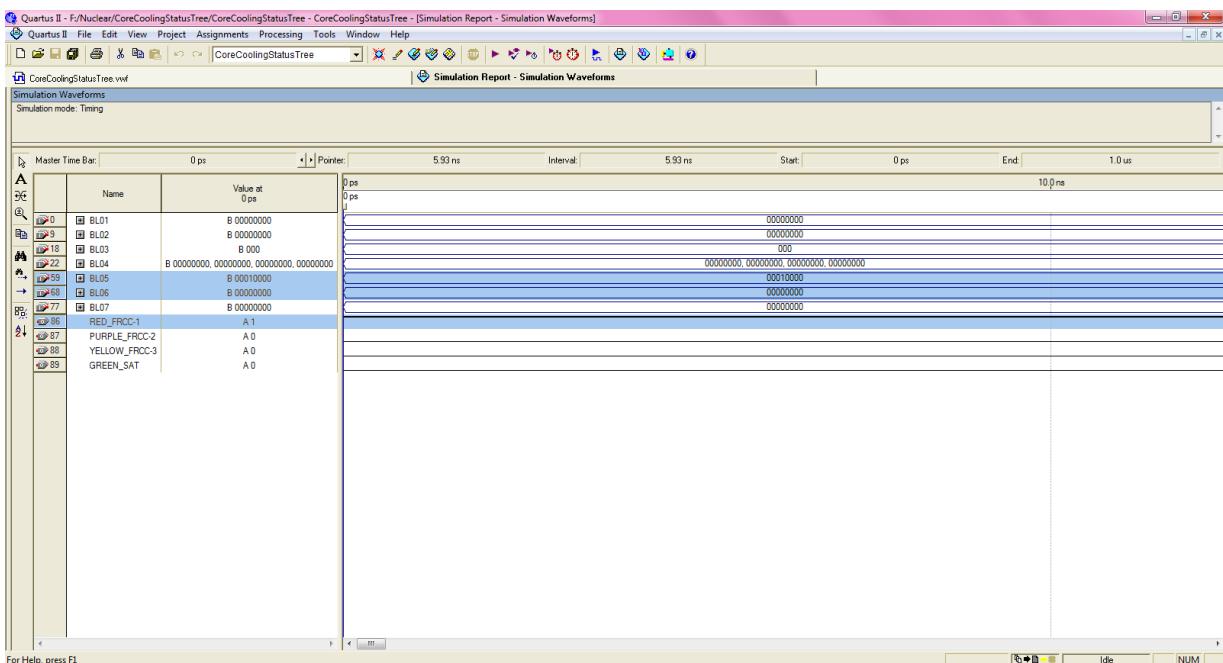

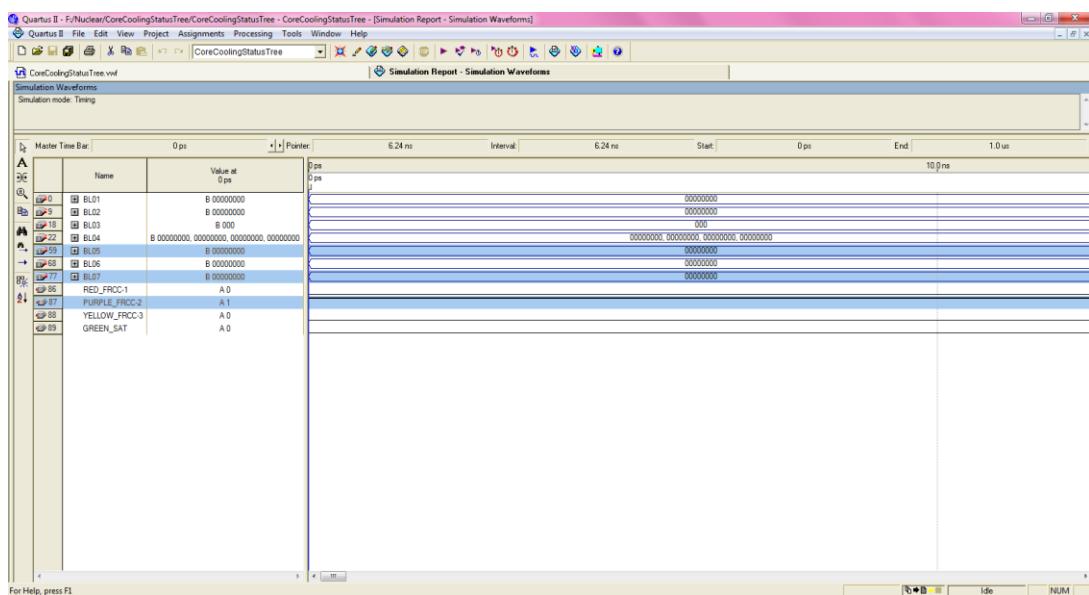

| Figura 31– Simulação do resultado RED_FRHS-1.....                      | 82 |

| Figura 32 – Simulação do resultado GREEN_SAT .....                     | 83 |

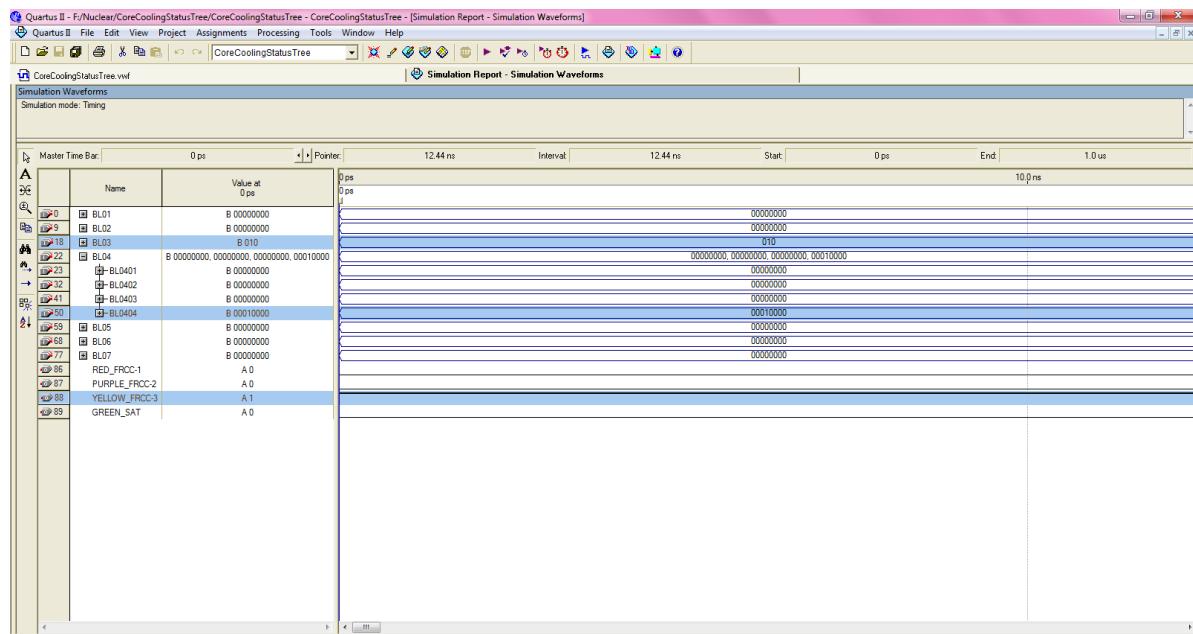

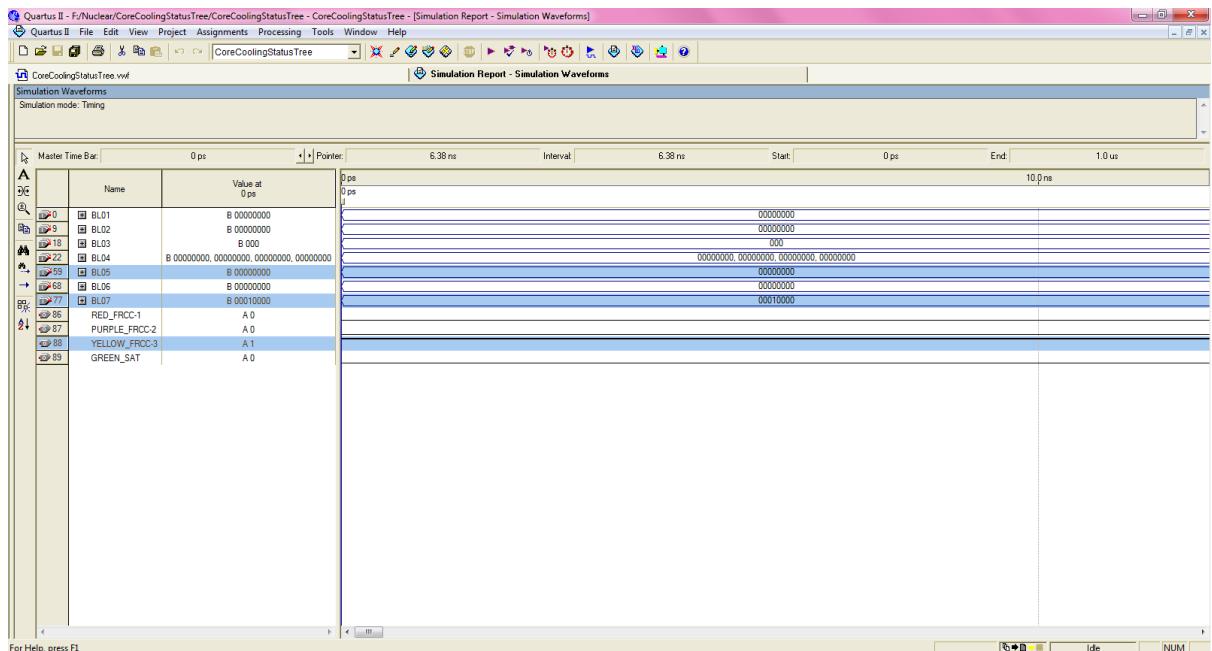

| Figura 33 – Simulação do resultado YELLOW_FRCC-3.....                  | 84 |

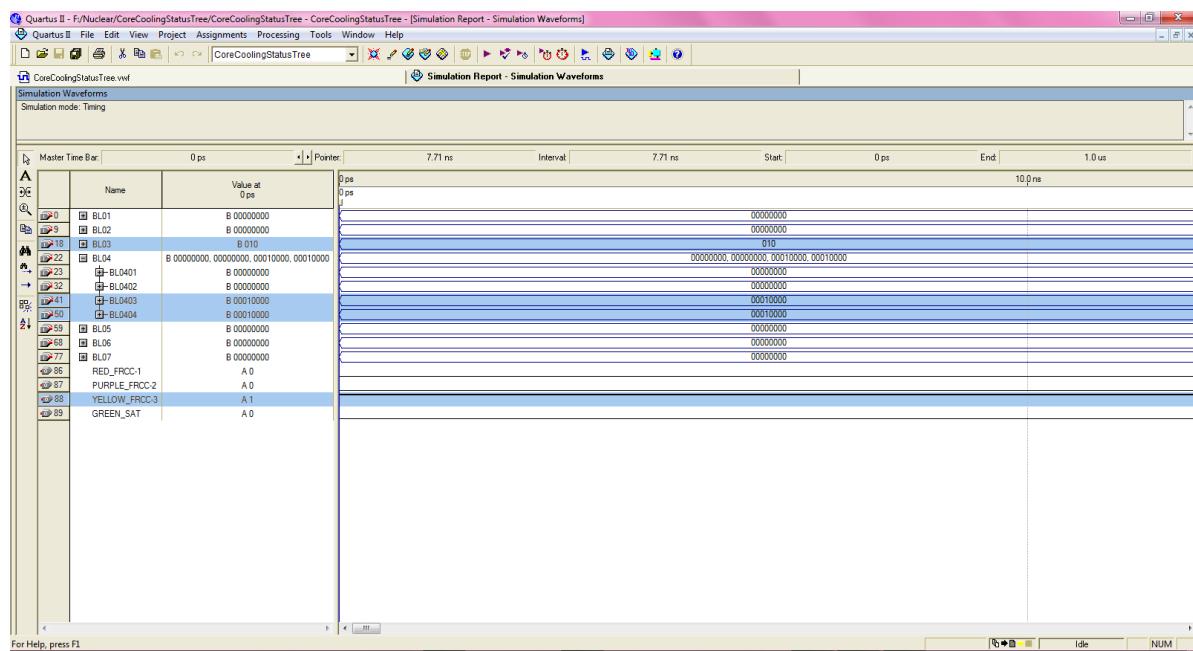

| Figura 34– Simulação do resultado YELLOW_FRCC-3.....                   | 84 |

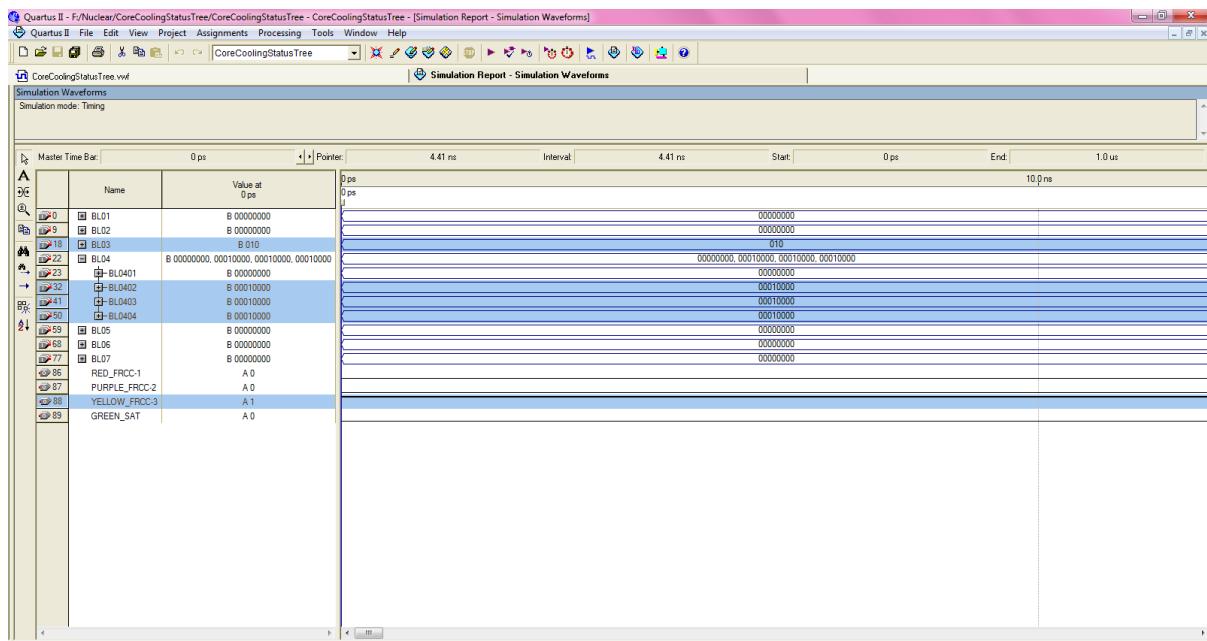

| Figura 35 – Simulação do resultado YELLOW_FRCC-3.....                  | 85 |

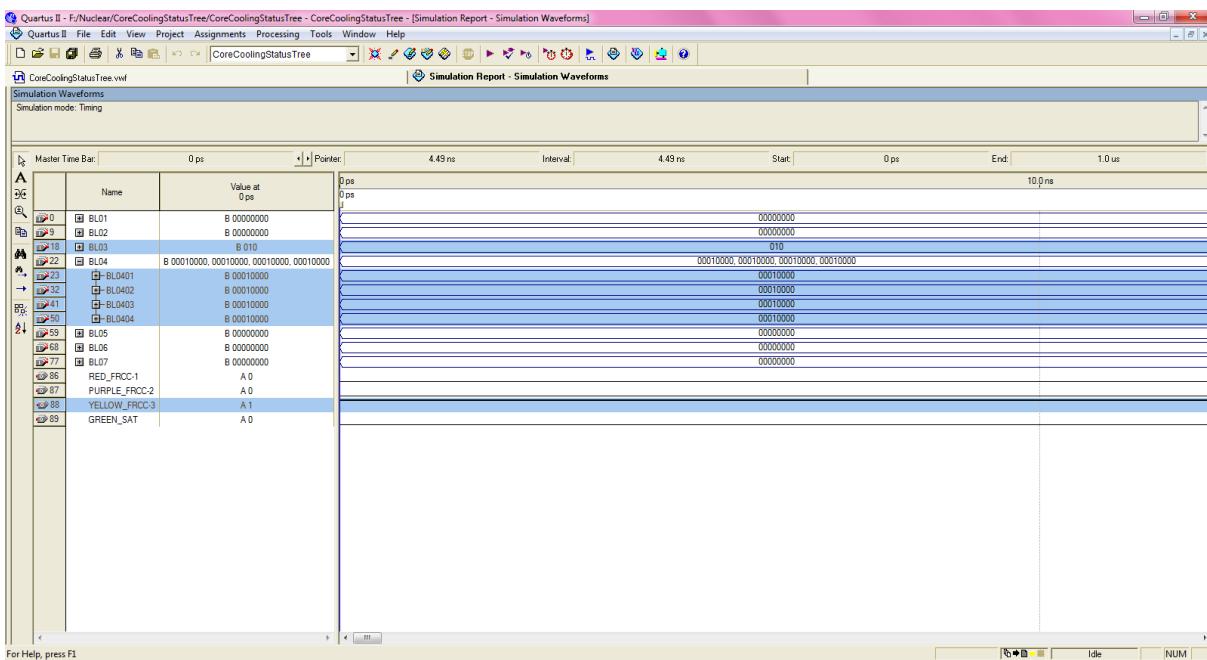

| Figura 36– Simulação do resultado YELLOW_FRCC-3.....                   | 85 |

| Figura 37– Simulação do resultado PURPLE_FRCC-3 .....                  | 86 |

| Figura 38– Simulação do resultado PURPLE_FRCC-3 .....                  | 87 |

| Figura 39– Simulação do resultado RED_FRCC-1.....                      | 87 |

| Figura 40– Simulação do resultado PURPLE_FRCC-2 .....                  | 88 |

| Figura 41– Simulação do resultado PURPLE_FRCC-2 .....                  | 88 |

| Figura 42– VHDL da FCS Resfriamento do Núcleo .....                    | 89 |

|                                                                        |     |

|------------------------------------------------------------------------|-----|

| Figura 43– Numeração dos blocos da FCS Transferência de calor.....     | 90  |

| Figura 44– Esquemático da FCS referente à Transferência de calor ..... | 93  |

| Figura 45 – Esquemático Bloco 1.....                                   | 95  |

| Figura 46– Esquemático Bloco2.....                                     | 96  |

| Figura 47– Esquemático Bloco 3.....                                    | 97  |

| Figura 48– Esquemático Bloco 4.....                                    | 98  |

| Figura 49– Esquemático Bloco5.....                                     | 99  |

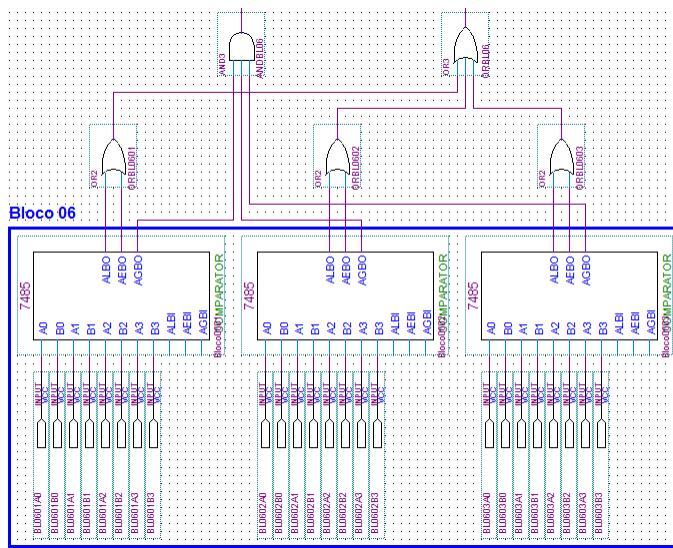

| Figura 50– Esquemático Bloco 6.....                                    | 100 |

| Figura 51– Agrupamento das Entradas do comparador BL0101 .....         | 101 |

| Figura 52– Agrupamento dos Comparadores do bloco 1.....                | 102 |

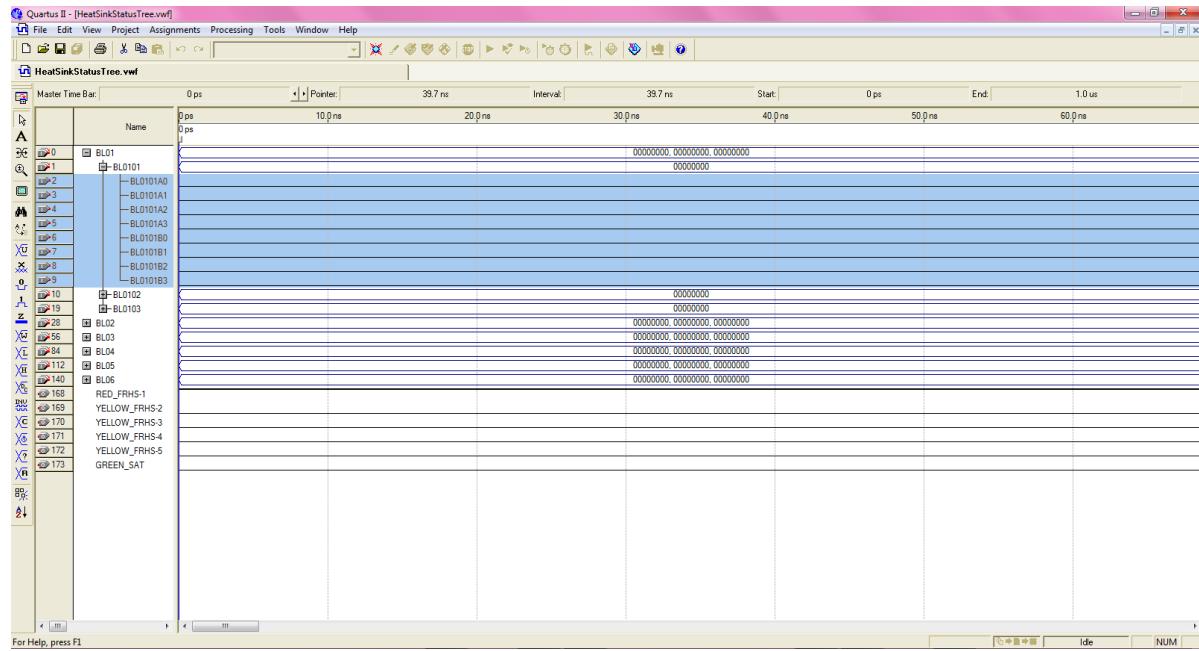

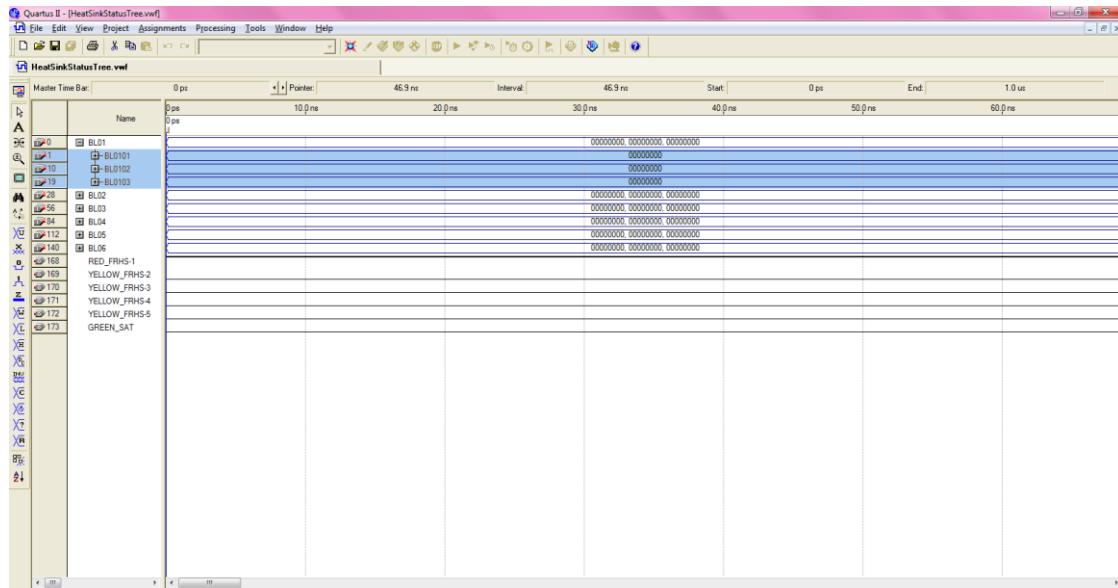

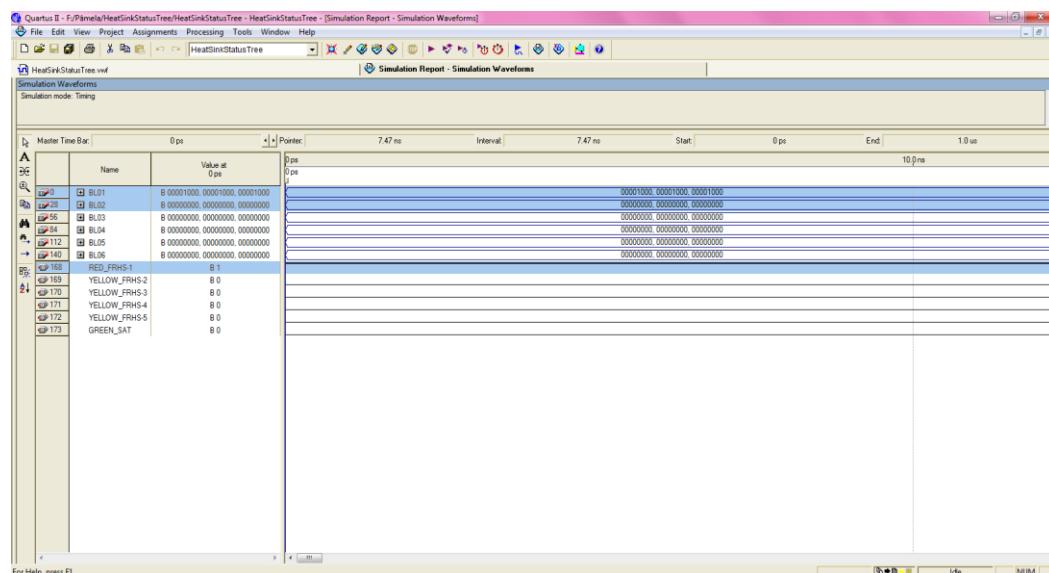

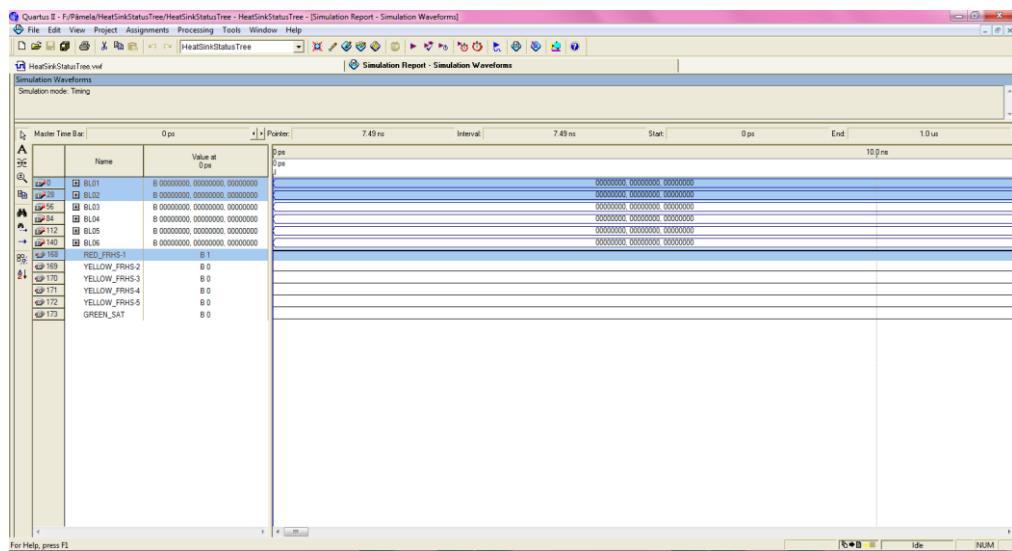

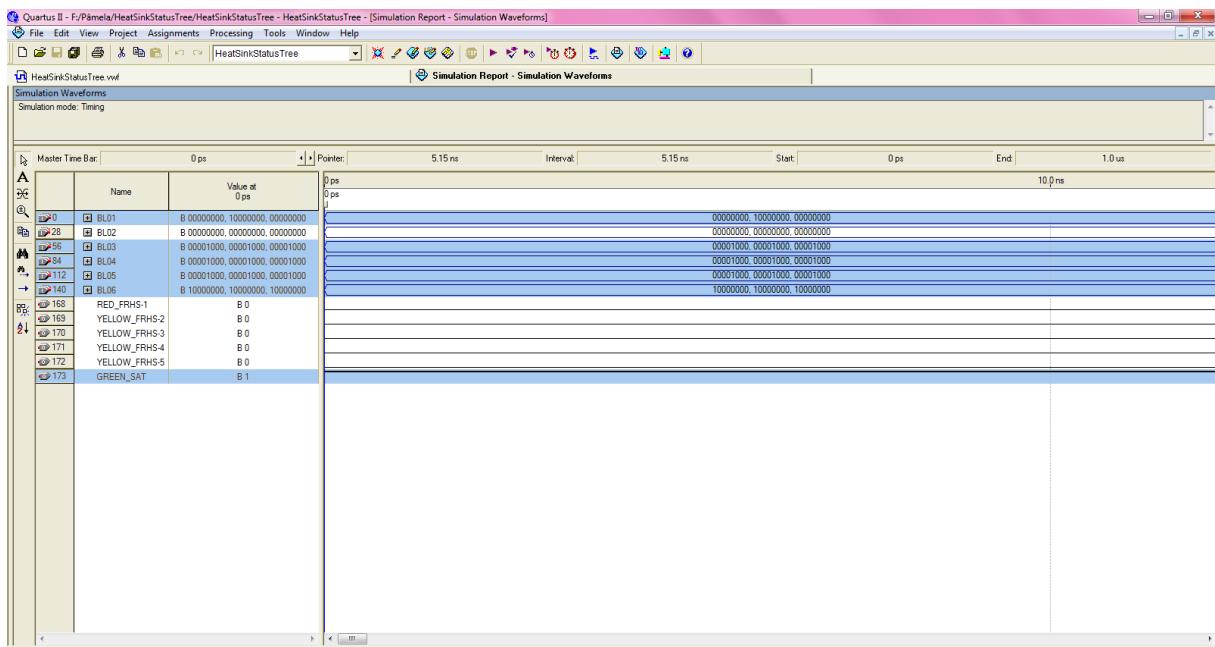

| Figura 53– Simulação do resultado RED_FRHS-1.....                      | 103 |

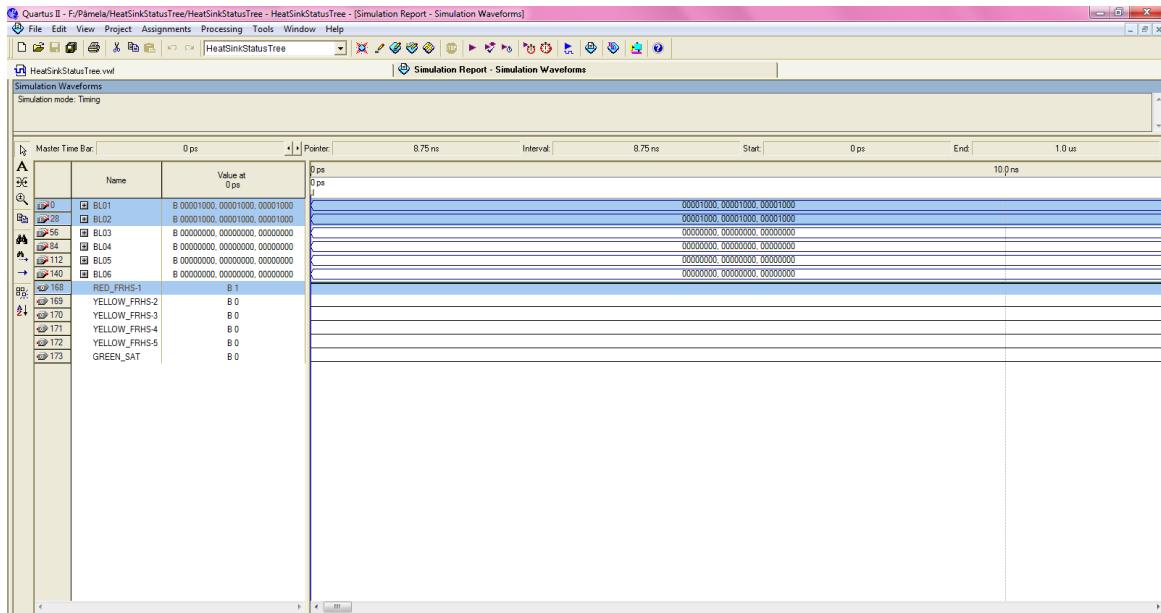

| Figura 54– Simulação do resultado RED_FRHS-1.....                      | 103 |

| Figura 55 – Simulação do resultado RED_FRHS-1.....                     | 104 |

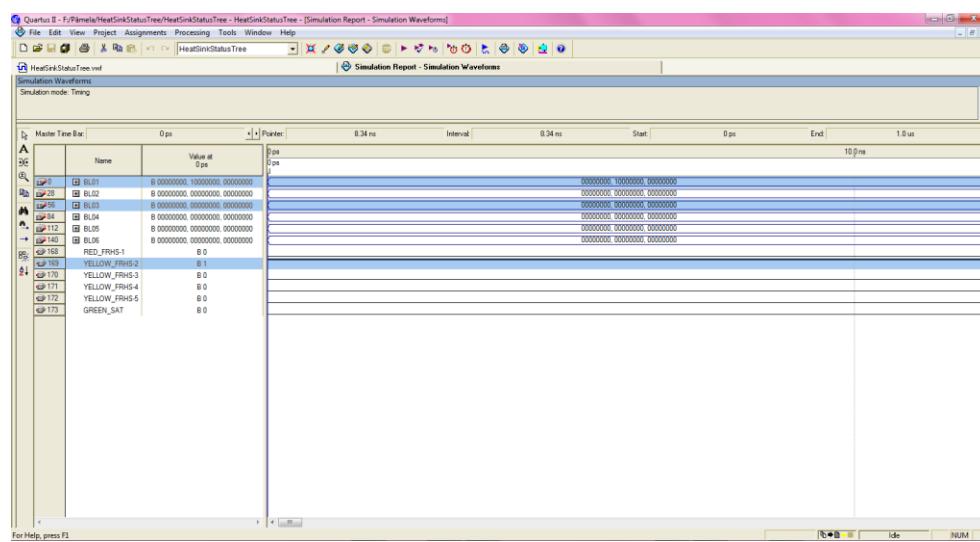

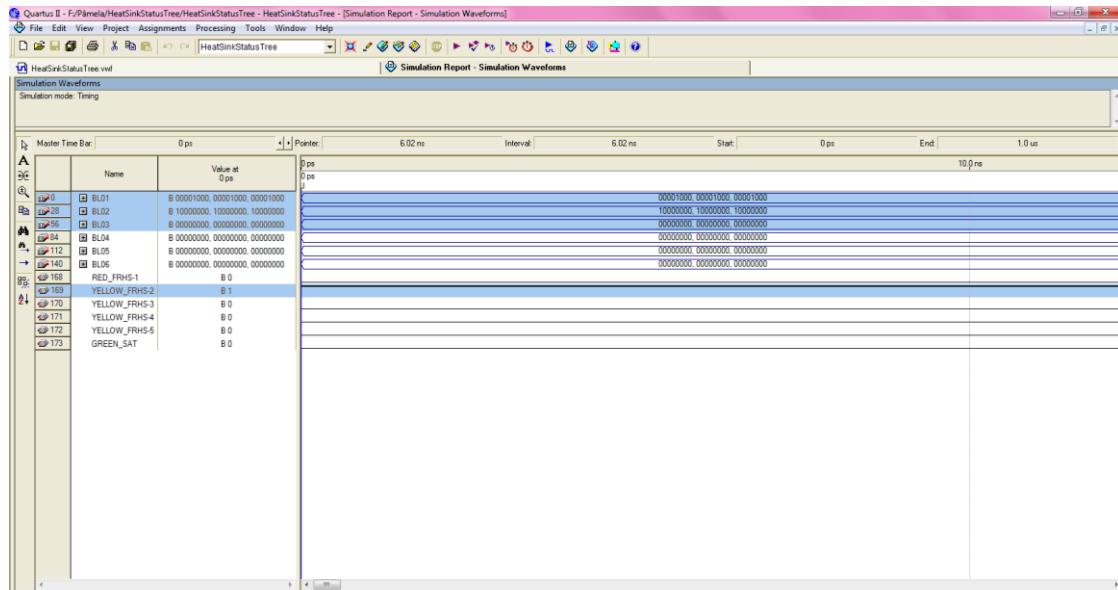

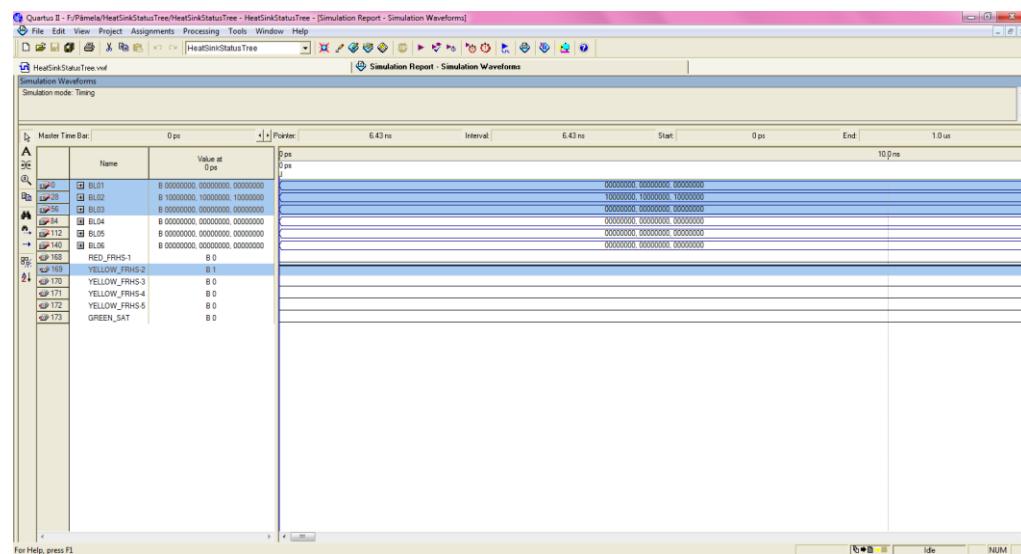

| Figura 56 – Simulação do resultado YELLOW_FRHS-2.....                  | 104 |

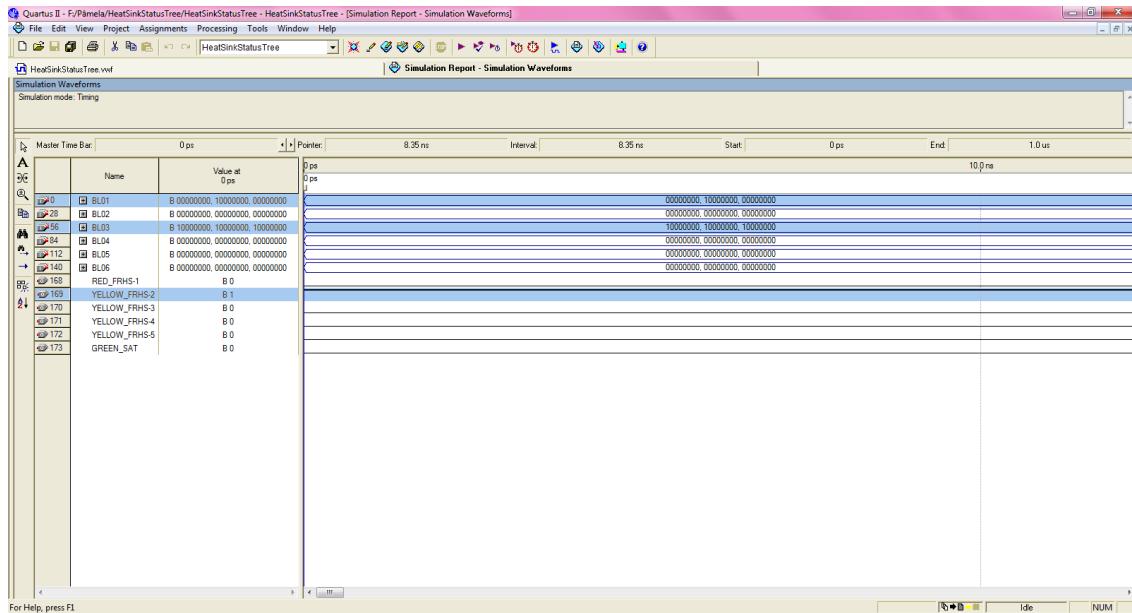

| Figura 57– Simulação do resultado YELLOW_FRHS-2 .....                  | 105 |

| Figura 58– Simulação do resultado YELLOW_FRHS-2 .....                  | 106 |

| Figura 59– Simulação do resultado YELLOW_FRHS-2 .....                  | 106 |

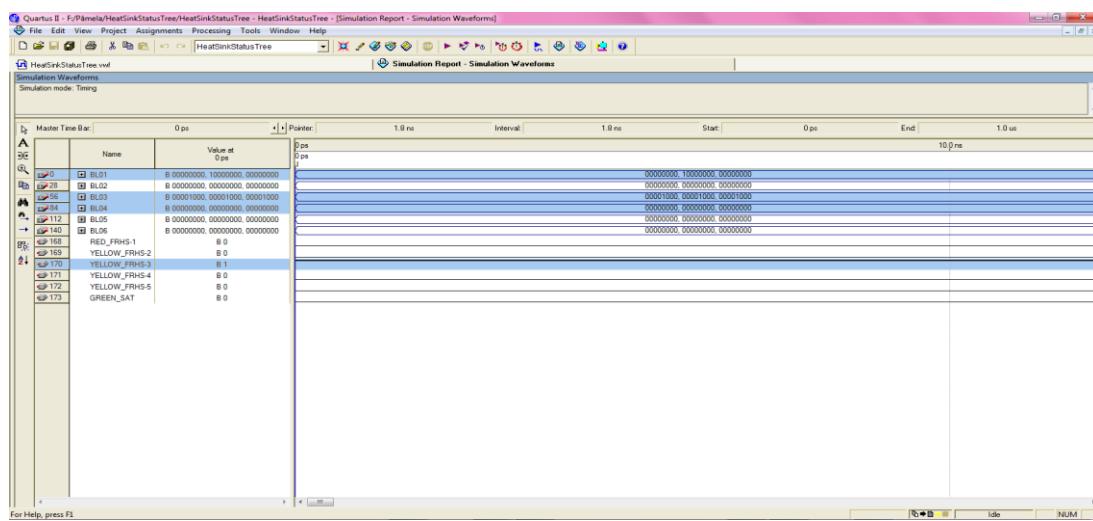

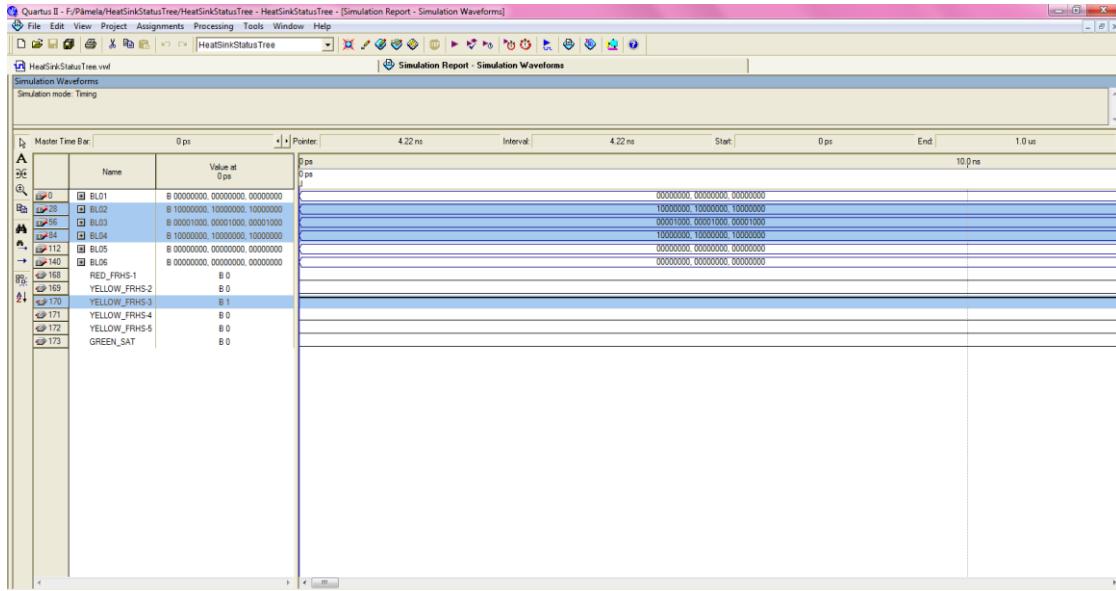

| Figura 60– Simulação do resultado YELLOW_FRHS-3.....                   | 107 |

| Figura 61– Simulação do resultado YELLOW_FRHS-3.....                   | 108 |

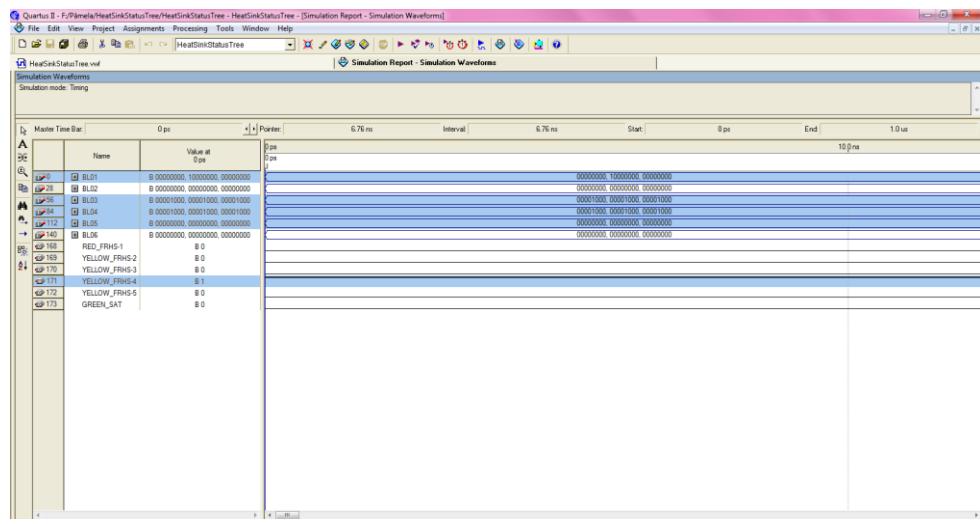

| Figura 62– Simulação do resultado YELLOW_FRHS-4.....                   | 109 |

| Figura 63 – Simulação do resultado YELLOW_FRHS-4.....                  | 110 |

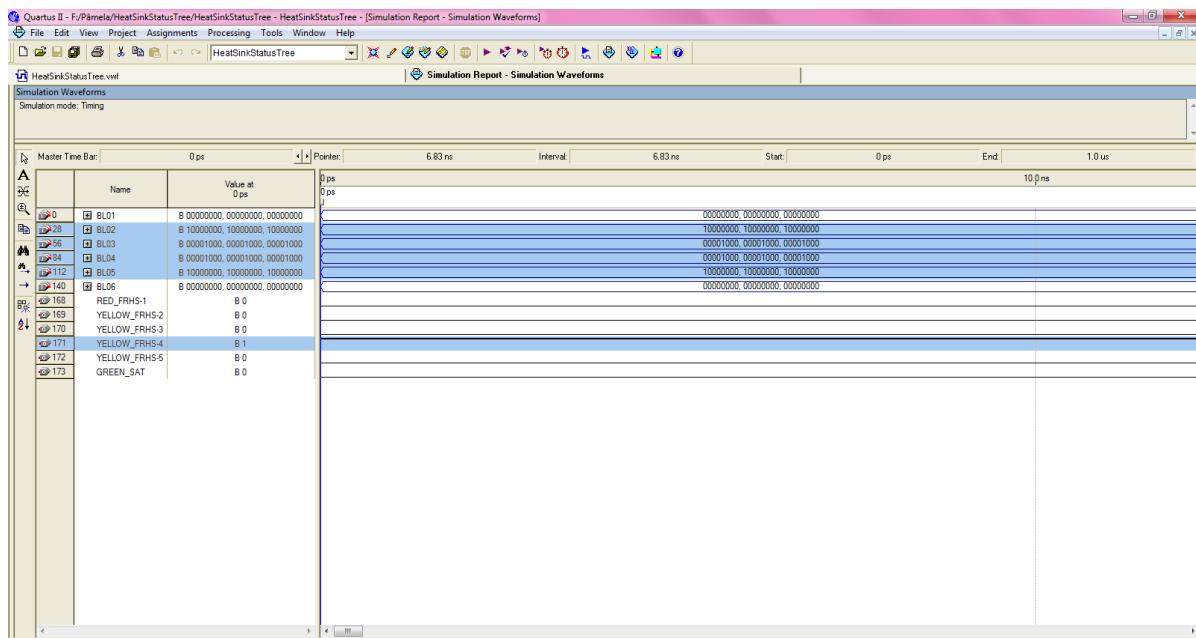

| Figura 64 – Simulação do resultado YELLOW_FRHS-2.....                  | 111 |

|                                                      |     |

|------------------------------------------------------|-----|

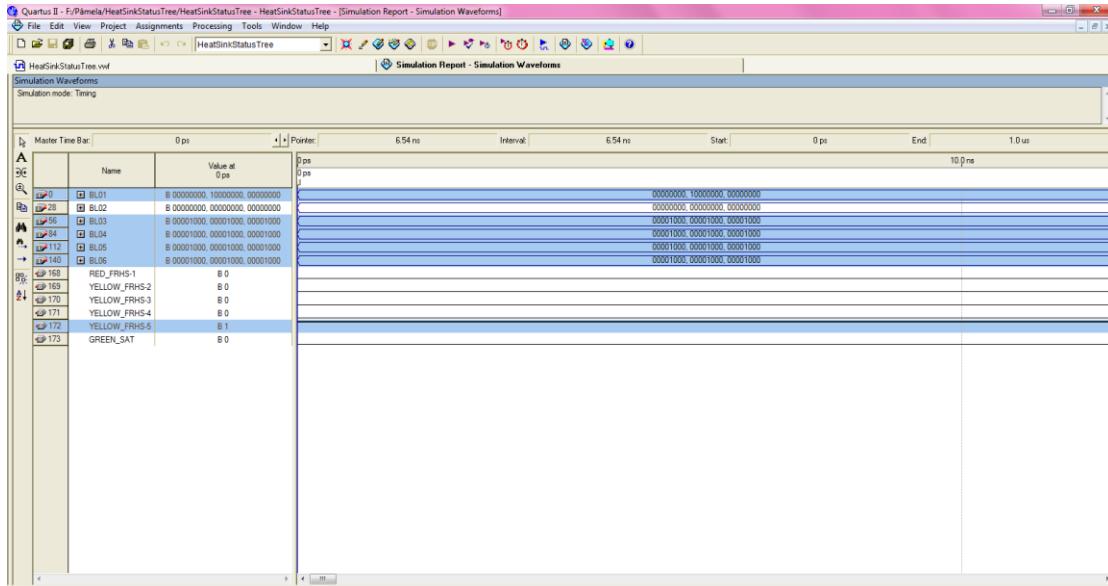

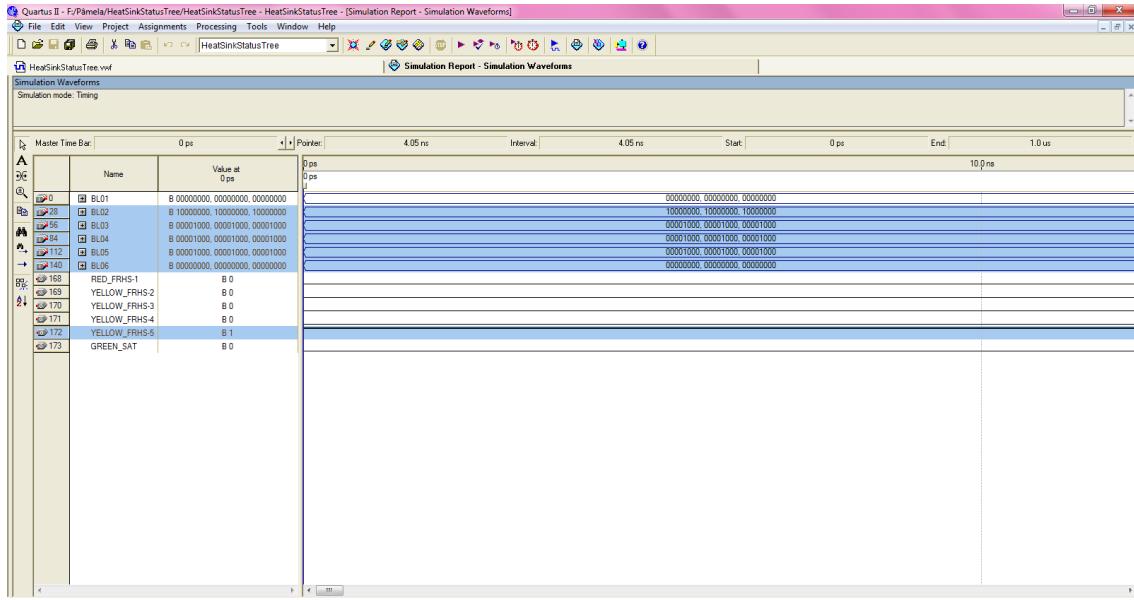

| Figura 65– Simulação do resultado YELLOW_FRHS-5..... | 112 |

| Figura 66– Simulação do resultado GREEN_SAT.....     | 113 |

| Figura 67– VHDL da FCS Transferência de Calor.....   | 114 |

## LISTA DE ABREVIATURAS

|        |                                                                |

|--------|----------------------------------------------------------------|

| AHDL   | (Altera Hardware Description Language)                         |

| ASIC   | ( <i>Application-Specific Integrated Circuit</i> )             |

| BC     | <i>Barra de Controle</i>                                       |

| CLB    | ( <i>Configurable Logic Block</i> )                            |

| CNEN   | Comissão Nacional de Engenharia Nuclear                        |

| DENN   | Divisão de Engenharia Nuclear                                  |

| EC     | Elemento Combustível                                           |

| EDIF   | ( <i>Electronic Interchange Format</i> )                       |

| EPLD   | ( <i>Erasable Programmable Logic Device</i> )                  |

| EEPROM | ( <i>Electrically Erasable Programmable Read Only Memory</i> ) |

| EPROM  | ( <i>Erasable Programmable Read Only Memory</i> )              |

| FCS    | Funções Críticas de Segurança                                  |

| FPGA   | ( <i>Field Programmable Gate Array</i> ).                      |

| GV     | Gerador de vapor                                               |

| HDL    | ( <i>Hardware Description Language</i> )                       |

| IAEA   | ( <i>International Atomic Energy Agency</i> )                  |

| ISH    | Interface de Sistema-Humano                                    |

| I/O    | Entrada /Saída                                                 |

| IEN    | Instituto de Engenharia Nuclear                                |

| IP     | ( <i>Intellectual Property</i> )                               |

|        |                                                    |

|--------|----------------------------------------------------|

| ISP    | ( <i>In System Programmability</i> ).              |

| KAERI  | ( <i>Korean Atomic Energy Research Institute</i> ) |

| LABIHS | Laboratório de Interfaces Homem-Sistema            |

| LUT    | ( <i>Look-Up Table</i> )                           |

| NRC    | ( <i>Nuclear Regulatory Commission</i> )           |

| PAR    | ( <i>Place And Route</i> ).                        |

| POE    | Procedimento Operacional de Emergência             |

| PWR    | ( <i>Pressurized Water Reactor</i> )               |

| RTL    | ( <i>Register Transfer Level</i> )                 |

| SD     | Sistema Digital                                    |

| SCPS   | Sistema Computacional de Parâmetros de Segurança   |

| SFCS   | Sistema de Funções Crítica de Segurança            |

| SIMP   | Sistema Integrado de Monitoração de Parâmetros     |

| SM     | Matriz de Ligação Configurável                     |

| SOP    | ( <i>Sun Of Products</i> )                         |

| SPDS   | Sistema de Monitoração de Parâmetros de Segurança  |

| SRAM   | ( <i>Static Random Access Memory</i> )             |

| SSPS   | Sistema de Supervisão de Parâmetros de Segurança   |

| TCL    | ( <i>Tool Command Language</i> )                   |

| TMI    | ( <i>Tree Mile Island</i> )                        |

| Vcc    | Tensão Corrente Contínua                           |

## VHDL Linguagem de Descrição de Hardware

## WOG (Westinghouse Owners Group)

## SUMÁRIO

|                                                                                            |    |

|--------------------------------------------------------------------------------------------|----|

| <b>CAPÍTULO1 INTRODUÇÃO .....</b>                                                          | 18 |

| 1.1    Contextualização .....                                                              | 18 |

| 1.2Motivação .....                                                                         | 19 |

| 1.3Objetivo .....                                                                          | 19 |

| 1.4        Organização do Trabalho .....                                                   | 20 |

| <b>CAPÍTULO2 FUNÇÕES CRÍTICAS DE SEGURANÇA.....</b>                                        | 22 |

| 2.1Descrição Geral dos Principais Componentes de uma Usina PWR e Barreia de Proteção ..... | 22 |

| <b>2.1.1Descrição resumida dos componentes do circuito primário .....</b>                  | 24 |

| <b>2.1.2Descrição resumida dos componentes do circuito secundário.....</b>                 | 25 |

| <b>2.1.3Descrição resumida dos componentes do circuito terciário.....</b>                  | 26 |

| 2.2        Barreiras Físicas de Proteção .....                                             | 27 |

| 2.3        O Acidente em Tree Mile Island .....                                            | 30 |

| 2.4        Sistema de Supervisão de Parâmetros de Segurança.....                           | 34 |

| 2.5        Sistema de Funções Críticas de Segurança .....                                  | 35 |

| 2.6        Definições de Funções Críticas de Segurança.....                                | 36 |

| <b>CAPÍTULO3 FIELD PROGRAMMABLE GATE ARRAY .....</b>                                       | 42 |

| 3.1        Dispositivo FPGA .....                                                          | 42 |

| 3.2        Uso de FPGA em Sistemas de Segurança Nuclear .....                              | 43 |

| 3.3        As Estruturas de m FPGA .....                                                   | 44 |

| <b>3.3.1Definição de blocos lógicos .....</b>                                              | 45 |

|                                                                                    |     |

|------------------------------------------------------------------------------------|-----|

| <b>3.3.2Núcleo de FPGA .....</b>                                                   | 48  |

| <b>3.3.3Desenvolvimento de projetos em FPGA .....</b>                              | 49  |

| <b>3.3.4 Arquitetura geral de roteamento .....</b>                                 | 51  |

| 3.4 FPGAS Comerciais .....                                                         | 52  |

| 3.5 FPGA na Indústria.....                                                         | 53  |

| 3.6 Linguagem de Descrição de Hardware(VHDL) .....                                 | 53  |

| <b>3.6.1Níveis de abstração e descrição .....</b>                                  | 54  |

| <b>3.6.2Componentes do VHDL .....</b>                                              | 55  |

| <b>CAPÍTULO 4FPGA NAS FUNÇÕES CRÍTICAS DE SEGURANÇA NO LABIHS .....</b>            | 57  |

| 4.1 Salas de Controle Digital.....                                                 | 57  |

| <b>4.1.1Sala de controle do simulador LABIHS .....</b>                             | 58  |

| <b>4.1.2Interface humano – sistema das funções crítica de segurança .....</b>      | 60  |

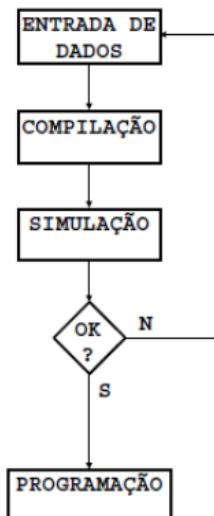

| 4.2 Simulador Quartus .....                                                        | 64  |

| <b>CAPÍTULO 5IMPLEMENTAÇÃO DAS FUNÇÕES CRÍTICAS DE SEGURANÇA USANDO<br/>FPGA..</b> | 67  |

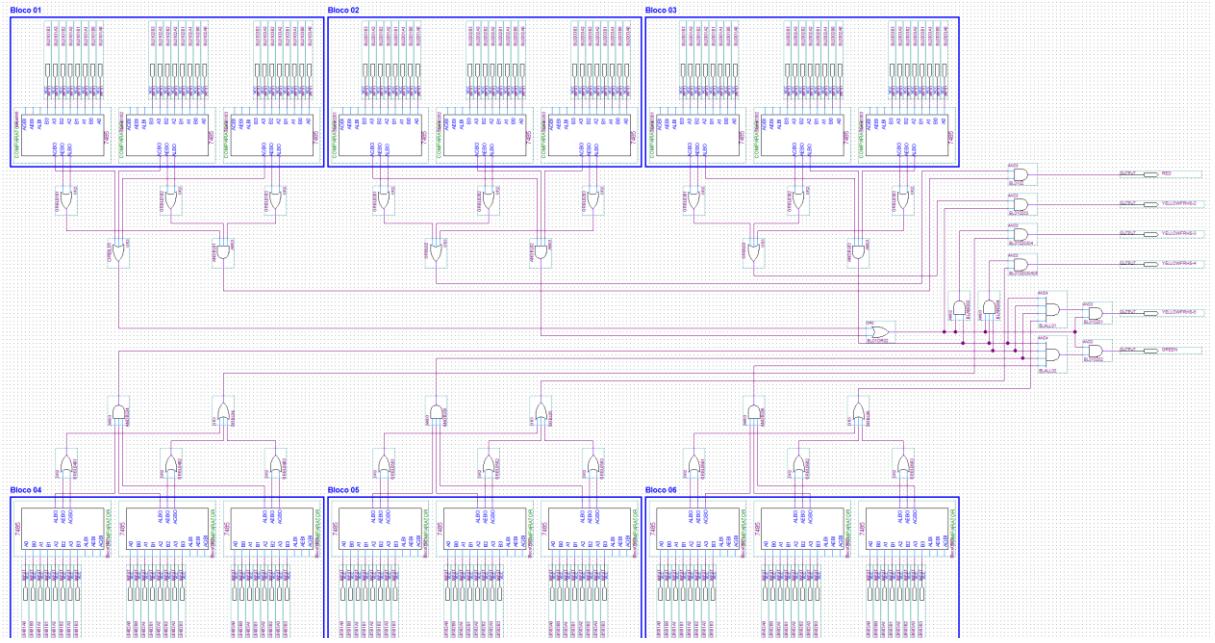

| 5.1 Avaliação da FSC Resfriamento do Núcleo .....                                  | 67  |

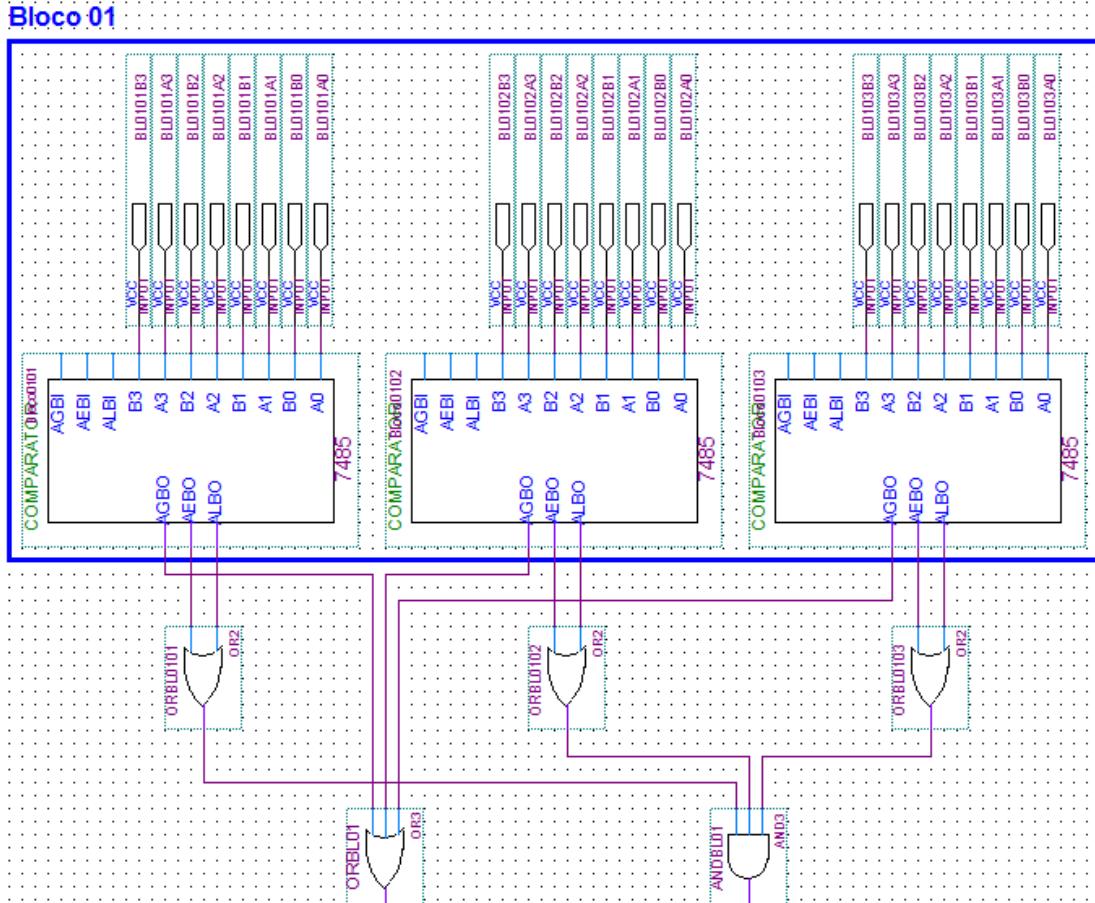

| <b>5.1.1Descrição do esquemático da FCS Resfriamento do Núcleo.....</b>            | 72  |

| <b>5.1.2Simulação FCS Resfriamento do núcleo.....</b>                              | 81  |

| <b>5.1.3VHDL da FCS Resfriamento do núcleo.....</b>                                | 89  |

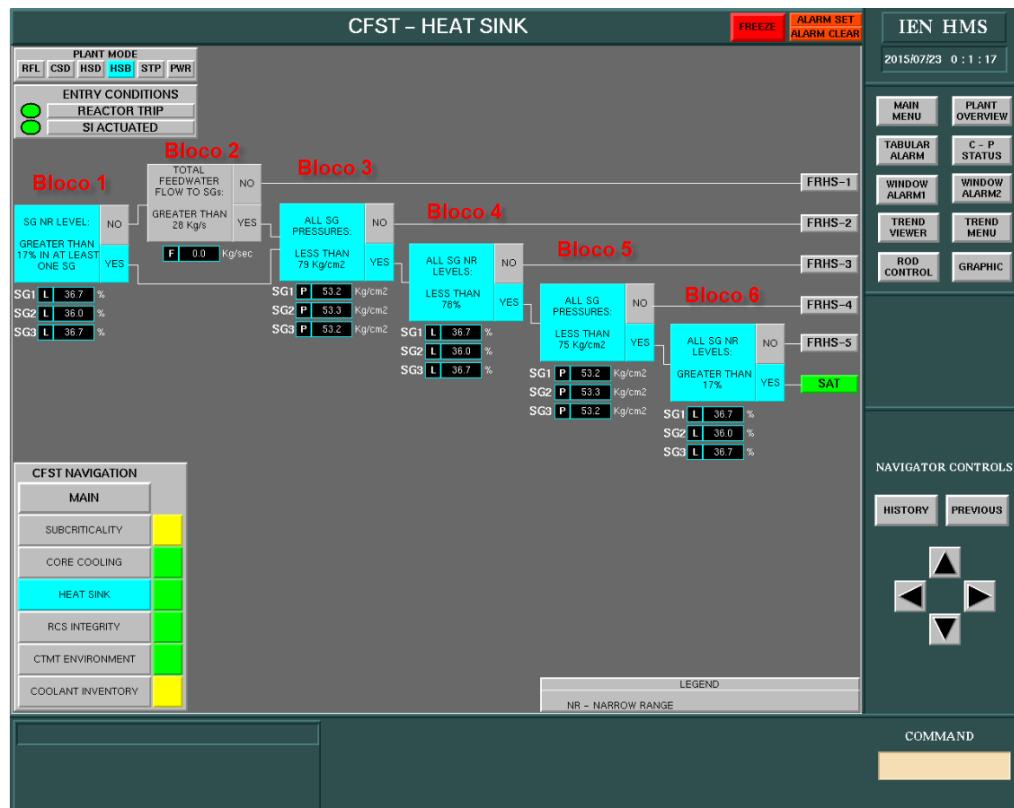

| 5.2 Avaliação da FSC: Transferência de Calor .....                                 | 90  |

| <b>5.2.1Descrição do esquemático da FCS Resfriamento do núcleo .....</b>           | 93  |

| <b>5.2.2Simulação FCS Transferência de calor .....</b>                             | 100 |

|                                                     |            |

|-----------------------------------------------------|------------|

| <b>5.2.3VHDL da FCS Transferência de Calor.....</b> | <b>114</b> |

| <b>6CONCLUSÃO .....</b>                             | <b>116</b> |

| <b>7REFERÊNCIAS BIBLIOGRÁFICAS.....</b>             | <b>117</b> |

## 1 INTRODUÇÃO

### 1.1 CONTEXTUALIZAÇÃO

Após o acidente na unidade dois da Central Nuclear de *Three Mile Island* (TMI) em 1979, foi evidenciada a necessidade de se melhorar de modo significativo a apresentação das informações sobre os principais parâmetros operacionais responsáveis pela segurança da central.

Foi sugerida a criação de um novo sistema baseado em um conjunto de funções críticas de segurança (FCS), que monitoram o grau de ameaça às barreiras de proteção da usina (IAEA-GSR, 2009).

Segundo a International Atomic Energy Agency (IAEA-GSR, 2009), as funções críticas de segurança são definidas como as funções necessárias para prevenir acidentes ou mitigar consequências mais graves de acidentes ainda durante a operação normal, antecipando assim ocorrências e condições de acidentes.

Atualmente os sistemas de funções críticas de segurança para reatores são tão importantes que são exigências para o licenciamento e operação das centrais (U.S-NRC, 2002).

## 1.2 MOTIVAÇÃO

Utilizando uma linguagem de descrição de circuitos possibilita várias aplicações, como no teste de circuitos e na síntese do circuito descrito. O Projeto de Programação em VHDL de Circuitos Lógicos para Implementação em FPGA está utilizando esta linguagem, pois a mesma pode suportar projetos com múltiplos níveis de hierarquias o que é muito importante para a aplicação inicial deste projeto. Os dispositivos de segurança incorporados ao projeto asseguram a possibilidade de controle de acidentes cuja ocorrência, embora extremamente improvável, é postulada como base de projeto.

A motivação para este trabalho surge a partir da possibilidade do desenvolvimento de novas formas de projeto de sistemas de funções críticas de segurança para reatores nucleares usando FPGAs..

Princípios de segurança baseados em recomendações de órgãos regulatórios internacionais são aplicados em todas as fases do projeto de uma usina nuclear. Desta forma, pode-se afirmar que a operação das usinas nucleares é segura e que a probabilidade de ocorrência de um acidente com consequência para o meio ambiente é extremamente reduzida em comparação com outras atividades industriais convencionais.

## 1.3 OBJETIVO

O objetivo desta dissertação é propor uma modelagem de funções críticas de segurança de reatores nucleares utilizando FPGA (*Field Programmable Gate Array*). Foi desenvolvida a modelagem para a Função Crítica Resfriamento do Núcleo e Função Crítica Transferência de Calor implementado por VHDL, que é uma forma de se descrever, através de um programa, o comportamento de um circuito ou componente digital. Para esta implementação foi utilizada a ferramenta Quartus II da Altera utilizada para a descrição, compilação, simulação do sistema.

Após implementadas, as aplicações de funções de segurança usando FPGAs são executadas sem software sistema em relação a sistemas dependentes de software. Essa funcionalidade, unida às funções críticas de segurança, seria um grande diferencial em relação à segurança, uma vez que as funções críticas têm uma estrutura hierárquica de informações das variáveis que afetam a segurança da planta. Quando ocorre uma emergência na central nuclear, o operador deve monitorar periodicamente as FCS e identificar possíveis caminhos de sucesso, para estabilizar ou desligar a planta usando procedimentos operacionais de emergência. Visando proporcionar um ambiente de informação amigável aos operadores Hunh Kim (Kim et al;2001) desenvolveu uma interface para apoiar a tarefa SFSC. A mesma consiste em três níveis hierárquicos de informação: a árvore de caminho incluindo funções de segurança e seus caminhos de sucesso, estrutura de fluxo do caminho de sucesso, estruturas topológicas do sistema relacionadas com o caminho de sucesso. Foi sugerido por Furuta (*Furuta et al;1999*) organizar hierarquicamente as informações ao longo de vários níveis da segurança da planta, pois isso ajudaria o operador a compreender essas funções na planta mais precisamente, e apoiar sua meta dirigida à resolução de problemas de adaptação.

Foi desenvolvido por Jun-Jen Lu (Jun-Jen Lu, et al;2015) um sistema de aplicação de backup para os sistemas digitais utilizando FPGA. Tal sistema é um importante meio de defesa contra falhas de software indetectáveis.

O processo de aprovação pode ser significativamente simplificado com o uso do FPGA. Vários projetos bem-sucedidos têm sido realizados em todo o mundo (Nakagawa,2008; Nguyen, 2008). Um exemplo interessante é documentado por Clarkson (2008), mostrando que US NRC levou apenas dois anos para concluir o processo de certificação, que é muito mais curto do que um baseado em software, que pode durar mais de 10 anos.

#### 1.4 ORGANIZAÇÃO DO TRABALHO

O presente trabalho está distribuído em seis capítulos, sendo o próximo, capítulo 2, destinado à apresentação das funções críticas de segurança. No capítulo 3 serão

apresentados conceitos de FPGA (*Field Programmable Gate Array*). O capítulo 4 destina-se à implementação das FCS utilizando FPGA. No capítulo 5 serão descritos os testes obtidos da implementação, e por fim, no capítulo 6 está a exibição das principais conclusões obtidas do trabalho realizado.

## 2FUNÇÕES CRÍTICAS DE SEGURANÇA

Este capítulo tem como objetivo apresentar o conceito de Sistema de Funções Críticas de Segurança (SFCS), que faz parte do Sistema de Supervisão de Parâmetros de Segurança (SSPS), um sistema computadorizado de monitoração em tempo real de parâmetros, que determina o status de segurança e de procedimentos de emergência para retorno da central nuclear à condição de operação normal quando da ocorrência de uma situação atípica.

Este sistema foi introduzido como resultado da experiência obtida com o acidente na unidade 2 na usina de *Three Mile Island*, para o gerenciamento de risco e consciência operacional.

### 2.1 DESCRIÇÃO GERAL DOS PRINCIPAIS COMPONENTES DE UMA USINA PWR E BARREIRA DE PROTEÇÃO

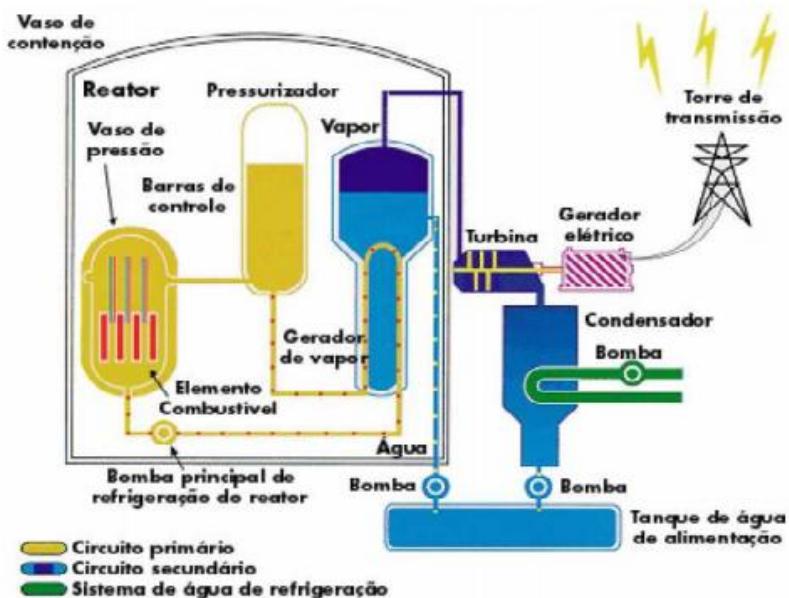

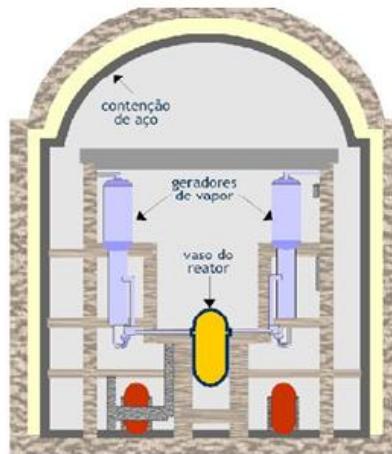

O reator a água pressurizada (PWR) é um reator que usa água leve para remoção do calor gerado pela fissão nuclear e para a moderação dos nêutrons liberados no processo de fissão nuclear. A água é desmineralizada e tratada quimicamente para torná-la um meio refrigerante apropriado para o reator. O PWR pode ser dividido em três circuitos termo-hidráulicos: primário, secundário e terciário. O circuito primário é composto basicamente pelo vaso do reator, parte primária do gerador de vapor (GV), bomba de circulação do refrigerante/moderador, pressurizador e tubulações associadas. O circuito secundário é composto pela parte secundária do GV, turbina que faz girar o gerador elétrico, parte secundária do condensador, e bomba de água de alimentação e tubulações associadas. O circuito terciário compõe-se do condensador (parte terciária) e da bomba de circulação da água do terciário, que no caso das plantas Angra I e II é alimentado pela água do mar. A figura 1 apresenta a vista pictórica de um PWR com seus principais componentes.

Figura 1– Representação da usina angra I (Adaptado CNEN)

A fissão dos átomos de urânio dentro das varetas do elemento combustível aquece a água que passa pelo reator. O gerador de vapor realiza uma troca de calor entre as águas deste primeiro circuito e a do circuito secundário, que são independentes entre si. Com essa troca de calor, a água do circuito secundário se transforma em vapor e movimenta a turbina que, por sua vez, aciona o gerador elétrico. Esse vapor, depois de mover a turbina, passa pelo condensador, é refrigerado pela água do mar, trazida por um terceiro circuito independente.

Na central nuclear de reator a água pressurizada (PWR), que é o tipo mais utilizado mundialmente (inclusive nas usinas Angra I e II), o reator é projetado para ter características de auto-regulação, isto é, com o aumento da temperatura da água de refrigeração do núcleo do circuito primário, há uma diminuição de potência térmica, funcionando como um controle automático da potência térmica gerada.

### 2.1.1 Descrição resumida dos componentes do circuito primário

- Vaso de pressão - O núcleo do vaso de pressão é composto de elementos combustíveis que contêm material físsil em baixas concentrações. O calor gerado nos elementos combustíveis é removido pela passagem sobre os mesmos do fluxo do refrigerante.

- Gerador de vapor - Os geradores de vapor (GVs) constituem a barreira entre o sistema de refrigeração do reator (circuito primário) e o circuito água/vapor (circuito secundário), e produzem vapor superaquecido que aciona o conjunto turbo - gerador. Eles são projetados como um trocador de calor, tipo feixe vertical de tubos em U, com circulação natural de água de alimentação.

- Pressurizador - O Pressurizador é um vaso ligado ao circuito primário que fica parcialmente cheio de água. Com o auxílio de aquecedores elétricos na parte cheia de água do pressurizador e um sistema de borrifo e alívio de pressão no espaço de vapor, regula-se a pressão do colchão de vapor do pressurizador e, portanto, a do sistema de refrigeração do reator, até um valor acima da pressão na qual o refrigerante se evaporaria, mantendo-a constante neste ponto.

- Bomba de recirculação do refrigerante - As bombas do circuito primário fazem a recirculação forçada da água refrigerante do circuito primário, garantindo a remoção do calor gerado dentro do vaso do reator pelo processo de fissão. Elas são do tipo centrífugas de um estágio e montadas verticalmente.

- Tubulação - A tubulação do circuito primário faz a interligação dos componentes do sistema de refrigeração do reator.

### 2.1.2 Descrição resumida dos componentes do circuito secundário

O vapor superaquecido, criado através do aquecimento adicional sobre o vapor úmido ou saturado, produzido pelo gerador de vapor, aciona as turbinas que são acopladas ao gerador elétrico para produzir energia elétrica. O vapor após passar pelas turbinas, é levado à fase líquida através do condensador. A água produzida pelo condensador é bombeada de volta ao gerador de vapor através do sistema de água de alimentação do circuito secundário.

- Gerador de vapor - A água de alimentação do GV entra pelo bocal localizado na parte superior do GV e é distribuída por um anel de alimentação para sua parte inferior onde se encontra o conjunto de tubos em U. Nesta parte do GV é efetuada a absorção do calor da água do circuito primário que circula pelos tubos em U. A água absorve o calor, gerando bolhas de vapor que sobem entre o conjunto de tubos em U para a parte superior do GV, onde um conjunto de separadores centrífugos de umidade, localizado acima do conjunto de tubos em U, remove a maioria da água de entrada do vapor. Placas perfuradas são incluídas na entrada do segundo estágio do separador. Secadores de vapor são empregados para aumentar a qualidade de vapor para um mínimo de 99,75% (0,25% de umidade). Um restritor de vazão de vapor é usado à saída do bocal de vapor para limitar a quantidade de fluxo de vapor, no caso de uma ruptura da linha de vapor.

- Turbina – As turbinas são acopladas mecanicamente ao gerador elétrico. Elas recebem o vapor superaquecido produzido nos GVs, que faz girar suas pás produzindo energia elétrica pelo gerador elétrico, que é enviada para a linha de transmissão da usina. Normalmente, numa planta tipo PWR existe uma turbina de alta-pressão e três de baixa-pressão. O vapor passa primeiramente pela de alta pressão, e é reaquecido antes de ser distribuído para as turbinas de baixa-pressão.

- Condensador e bombas de água de alimentação - O vapor, após passar pelas turbinas, é encaminhado para o condensador, a fim de ser levado de volta para a fase líquida para ser bombeado novamente para os GVs pelas bombas de água de alimentação.

- Tubulação - A tubulação do circuito secundário faz a interligação dos componentes do sistema do circuito secundário.

### **2.1.3 Descrição resumida dos componentes do circuito terciário**

O circuito terciário é responsável por absorver o calor do circuito secundário através do trocador de calor do condensador que efetua a condensação do excesso de vapor deste circuito.

- Condensador – O condensador tem como finalidade condensar o excesso de vapor gerado no circuito secundário (saída da turbina). Ele é dividido em duas partes: Uma onde passa o vapor que sai das turbinas e outra onde passa a água de resfriamento, destinada a baixar a temperatura interna do condensador. O vapor aquecido entra no condensador e encontra uma superfície com uma temperatura inferior ao seu ponto de ebulição e, então, condensa (ou liquefaz). Esse terceiro circuito normalmente retira água do mar, que, por ser salgada, possui características físico-químicas ideais quanto ao seu ponto de ebulição (mais alto que 100°C), sendo um dos motivos pelos quais a maioria das usinas nucleares é próxima ao mar.

- Bomba de circulação da água do mar – é responsável por circular a água do mar ou de uma torre de resfriamento pelo circuito terciário da usina.

## 2.2 BARREIRAS FÍSICAS DE PROTEÇÃO

Numa usina nuclear de potência existem sistemas de proteção ativos e passivos. Os sistemas de proteção ativos utilizam atuadores elétricos e mecânicos que são acionados quando é violada uma condição de segurança da planta. Esses sistemas utilizam energia elétrica fornecida pela rede de alimentação externa da planta ou sistemas de alimentação elétrica de emergência que são acionados no caso de falta de alimentação externa.

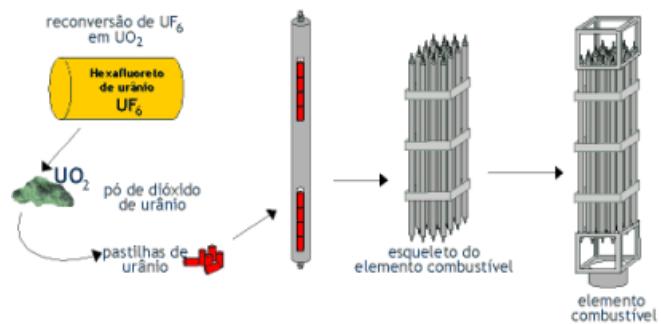

Os sistemas de proteção passivos da planta nuclear do tipo PWR são chamados de barreiras físicas de proteção e são: revestimento das pastilhas de combustível, varetas de combustível, vaso do reator e o prédio da contenção.

A primeira barreira física de proteção é o revestimento das pastilhas combustíveis. Para seu uso como combustível em reatores nucleares, o  $UF_6$  produzido com urânio enriquecido no isótopo  $^{235}U$  deve ser convertido em pó de dióxido de urânio ( $UO_2$ ), que então é processado, dando-lhe a forma de pequenas partículas. As partículas são comprimidas e cozidas a altas temperaturas, em um processo chamado sinterização, durante o qual as partículas se aderem entre si, formando pequenos cilindros (*pellets*) cerâmicos de urânio enriquecido. Os *pellets* cilíndricos então são retificados em tornos especiais, para obtenção de um tamanho uniforme.

A segunda barreira física de proteção é a vareta de combustível que serve para impedir a saída de material radioativo para o meio ambiente. Essas varetas são fechadas, com o objetivo de não deixar escapar o material nelas contido (o urânio e os elementos resultantes da fissão) e podem suportar altas temperaturas. Os elementos resultantes da fissão nuclear (produtos de fissão ou fragmentos da fissão) são radioativos, isto é, emitem radiações e, por isso, devem ficar retidos no interior do Reator.

Figura 2— Representação da vareta e elemento combustível (Adaptado CNEN 2003)

Na estrutura do Elemento Combustível (EC) existem tubos guias, por onde podem passar as Barras de Controle (BC), geralmente feitas de cádmio, material que absorve nêutrons, com o objetivo de controlar a reação de fissão nuclear em cadeia.

Normalmente, quando as barras de controle estão totalmente retiradas, o reator está na sua capacidade máxima de energia térmica. Quando elas estão totalmente inseridas na estrutura do EC, o reator está desligado (não há reação de fissão em cadeia).

Figura 3— Representação do elemento combustível (Adaptado CNEN 2003)

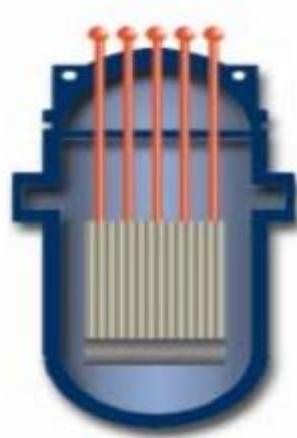

A terceira barreira física de proteção é o vaso de pressão onde estão situados os elementos combustíveis. O vaso de pressão serve para impedir a saída de material radioativo para o ambiente da contenção. O vaso do reator é fabricado com liga aço manganês molibdênio, que é usado tendo em vista a sua alta resistência e operação satisfatória em campos intensos de nêutron e raios gama. Sua superfície interna é folheada com um mínimo de 1/8 de polegada (0,32 cm) de solda de aço inoxidável austenítico para minimizar a formação de produto de corrosão.

Figura 4— Representação da contenção (Adaptado CNEN 2003)

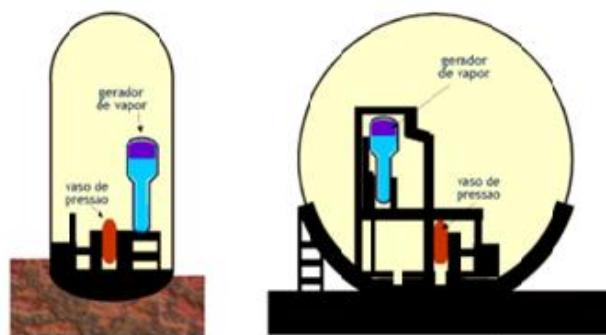

A quarta barreira física de proteção é o prédio da contenção, onde estão instalados todo o circuito primário e parte do circuito secundário do reator. A contenção serve para impedir a liberação de material radioativo - contido na água desses circuitos na forma de gases ou vapor de água - para o meio ambiente. Para dificultar a liberação de material radioativo na forma gasosa ou de vapor, a pressão no interior da contenção é mantida inferior à pressão atmosférica, que em caso de fissuras na contenção, ao invés de os gases e vapores saírem, é o ar externo que entra na contenção. A contenção também protege o reator de impactos externos como quedas de aviões, explosões etc.

O edifício da contenção é composto de um invólucro de aço recoberto por uma envoltória de concreto. A figura 5 apresenta uma vista pictórica da contenção metálica das usinas de Angra. Em Angra I, o edifício da contenção tem a forma cilíndrica e a de Angra II a forma esférica. A figura 5 apresenta uma vista pictórica do prédio da contenção de Angra I.

Figura 5— Representação do edifício do reator (Adaptado CNEN 2003)

Enquanto estiverem intactas as quatro barreiras anteriormente descritas, a usina nuclear não oferecerá nenhuma ameaça à segurança da população.

Se uma das barreiras for violada, a ameaça aumenta, tornando-se mais grave na medida em que for aumentando o número de barreiras violadas.

Quando todas as barreiras forem violadas, serão necessárias ações de emergência como, por exemplo, a evacuação da população local.

### 2.3 O ACIDENTE EM TREE MILE ISLAND

O acidente na unidade dois da Central Nuclear de *Three Mile Island* (TMI) 1979, nos Estados Unidos, foi iniciado por problemas mecânicos e de manutenção e acentuado por ações humanas inadequadas (KEMENY, 1979). Contribuíram para estas ações inadequadas problemas nos painéis da sala de controle e da instrumentação, que

dificultaram o entendimento do que realmente ocorria na planta, além da falta de coordenação das atividades dos operadores.

A seguir é descrita a sequência de eventos do acidente:

- A unidade 2 da Planta Nuclear *Three Miles Island* (TMI-2) operava normalmente com 97% (2.772 megawatts) de potência, no modo automático de controle da potência.

- (04h00min) Ocorreu um problema numa bomba do sistema de resfriamento do reator.

- A pressão e a temperatura dentro do reator começaram a subir, o que ocasionou (como esperado) a abertura da válvula de liberação (ou alívio) de pressão.

- Com o nível de pressão voltando ao normal, a válvula de liberação de pressão deveria ser automaticamente fechada, o que não ocorreu. Os operadores não perceberam que a válvula estava emperrada, (não completamente fechada por problemas mecânicos) o sistema indicava que havia sido enviado um sinal de “fechar” para a válvula. Todavia, o sistema não informava o estado correto da posição da válvula. Durante duas horas, com a válvula de liberação de pressão aberta, a água que resfria o núcleo evaporou para a atmosfera.

- Os operadores não interpretaram corretamente as leituras dos parâmetros de operação e controle da planta (pensavam que a alta temperatura seria temporária) e pararam o fluxo de emergência de água para o resfriamento do núcleo do reator.

- Em resposta à falta de água, as bombas de injeção de alta pressão automaticamente foram acionadas e começaram a adicionar água no sistema de resfriamento, quem desse assim continuava vazando vapor pela válvula de liberação de pressão (que permaneceu aberta).

- Os operadores imaginaram então que o núcleo estava com água em excesso (no treinamento, eles foram ensinados que somente água em excesso aumenta a pressão no núcleo) e diminuíram o fluxo de água para o resfriamento de emergência.

- Em virtude da falta de água, as bombas começaram a bombear uma mistura de água e vapor. Essa mistura fazia com que as bombas (e toda a planta) vibrassem o que poderia causar um dano maior à planta.

- Como pensavam que o reator tinha água em abundância, os operadores resolveram desligar todo o sistema de refrigeração (inclusive o resfriamento).

- Sem água temperatura subiu no núcleo do reator a ponto de fazer o urânio derreter dentro do vaso do reator (o maior dano do acidente) e contaminar a água de refrigeração com material radioativo.

- (06h22min) Os operadores conseguiram fechar uma válvula entre a bomba de liberação de pressão e o reator. Isso fez com que parasse o vazamento de água.

- (19h50min) Os operadores restauraram a normalidade a partir da injeção em alta pressão de água no sistema de resfriamento.

Mesmo que o acidente não tenha ocasionado nenhuma vítima fatal e tenha sido mantido dentro dos limites da contenção pelos sistemas que foram projetados para esta finalidade, a necessidade de deslocamento de grandes contingentes populacionais e o clima de especulação dado pela imprensa durante a evolução do

acidente (bolha de hidrogênio, liberação de produtos de fissão para o meio ambiente), fizeram com que o público tomasse consciência que reatores nucleares, tal como qualquer outra máquina desenvolvida pelo homem, podem sofrer acidentes.

Outra lição que TMI2 trouxe para a indústria nuclear foi a maneira de operar reatores nucleares, bem como uma reformulação da análise de acidentes em vista da possibilidade concreta de fusão do núcleo. Com relação à operação, houve a necessidade da reformulação da interação humano-sistema, fazendo com que o controle da evolução de um acidente passasse a ter a mínima interferência possível do operador. Foi adotado o procedimento de fornecer informações ao operador sobre o andamento dos parâmetros de segurança da planta durante um acidente e diagnósticos sobre as ações a serem tomadas.

De acordo com Kemeny (KEMENY, 1979), as salas de controle das usinas da geração de TMI-2 não eram projetadas para as necessidades da cognição do operador, pois os mesmos eram sobrecarregados com muitos alarmes, as informações necessárias não eram apresentadas de maneira conveniente e inteligível.

A resposta a esses problemas possibilitou uma reavaliação da segurança em toda a indústria nuclear, em projetos de plantas, acidentes de base de projeto, treinamento de pessoal, procedimentos de emergência e principalmente na interface humano - sistema; sendo uma das principais consequências a revisão do projeto das salas de controle que continham muitas informações dificultando a tomada de decisão para o operador (NUREG-0585, 1979).

Foram feitas algumas revisões (US.NRC,2007) em todas as usinas dos EUA em aspectos de interface humano-sistema. Foi revista a apresentação das informações nos displays procurando sua otimização em condição de operação normal,anormal e de emergência, bem como a comunicação entre os operadores da sala de controle,a operação da usina com múltiplas falhas e a adequação dos procedimentos operacionais às condições de limitações da instrumentação .

Através dos estudos feitos por Kemeny (KEMENY, 1979) e Nureg (NUREG-0585, 1979) (US.NRC,2007) as plantas da geração seguinte passaram a incorporar

sistemas para detectar e mitigar o resfriamento inadequado do núcleo e fornecer informações das condições pós-accidentes. Além disso, as salas de controle passaram a ser projetadas levando em conta aspectos cognitivos dos operadores.

Em resumo podemos dizer que o acidente de TMI-2 e as investigações consequentes evidenciaram a necessidade de se melhorar a apresentação das informações sobre os principais parâmetros operacionais relacionados à segurança da central nuclear.

A NRC formulou uma série de recomendações para melhorar as condições de atuação dos operadores, as quais estão contidas no NUREG-0585 (3) ("TMI Lessons Learned, TaskForce Final Report"). Dentre as referidas recomendações, destaca-se a da implementação em médio prazo de um sistema de auxílio ao operador intitulado Sistema de Supervisão de Parâmetros de Segurança (SSPS).

## 2.4 SISTEMA DE SUPERVISÃO DE PARÂMETROS DE SEGURANÇA

O Sistema de Supervisão de Parâmetros de Segurança (SSPS) é um sistema computadorizado de monitoração em tempo real dos parâmetros essenciais para a determinação do status de segurança e de procedimentos de emergência para retorno da central nuclear à condição de operação normal quando da ocorrência de uma situação atípica.

O SSPS é composto de três subsistemas distintos: O Sistema Integrado de Monitoração de Parâmetros (SIMP), o Sistema de Funções Críticas de Segurança (SFCS) e o Sistema Computacional de Parâmetros de Segurança (SCPS). O primeiro destina-se a dar aos operadores uma visão integrada dos valores de um conjunto de parâmetros, capaz de refletir qualquer desvio de operação normal da central.

O segundo fornece aos operadores um meio conveniente e eficaz para avaliação do status de segurança em termos de um conjunto prefixado de funções críticas de segurança. Em caso de violação de qualquer função crítica, o SFCS inicia

automaticamente o procedimento de emergência adequado para retorno da central a uma condição segura.

O terceiro subsistema realiza a aquisição dos sinais analógicos e digitais de controle da usina. Além disso, tem como finalidade fazer a validação dos sinais, impedindo que sinais falhos sejam apresentados ao operador através dos sistemas SIMP e SFCS.

Neste capítulo iremos dar ênfase ao segundo subsistema (SFCS) para que possamos ter um melhor entendimento sobre as Funções Crítica de Segurança.

## 2.5SISTEMA DE FUNÇÕES CRÍTICAS DE SEGURANÇA

O Sistema de Funções Críticas de Segurança (SFCS) é um subsistema do Sistema de Supervisão de Parâmetros de Segurança (SSPS). A concepção do SFCS baseia-se fundamentalmente na monitoração computadorizada em tempo real de um conjunto de funções denominadas "Funções críticas de segurança", especificadas por exemplo nos guias de respostas de emergência (4) (*Emergency Response Guidelines*) publicados pelo *Westinghouse Owners Group (WOG)*.

Os objetivos do SFCS consistem em fornecer ao operador:

- Uma avaliação continua do status de segurança da central em situações de operação de emergência, através da monitoração em tempo real de um conjunto de arranjos lógicos de parâmetros (árvores de estado) que compõem as chamadas funções críticas de segurança.

- A priorização das ações a serem executadas pelo operador em situações de emergência.

- Os procedimentos de operação de emergência necessários para o retorno da central a uma condição segura.

- Elementos auxiliares para ajudar o operador no cumprimento das tarefas estipuladas nos procedimentos, bem como acompanhar em tempo real os efeitos de suas ações sobre os diversos parâmetros e sistemas de segurança da central.

## 2.6 DEFINIÇÕES DE FUNÇÕES CRÍTICAS DE SEGURANÇA

As funções críticas de segurança (FCS) priorizam as ações do operador em função da potencial ameaça para as três barreiras (revestimento de combustível, fronteira do sistema de arrefecimento primário, e de contenção) e permite ao operador responder a estas ameaças antes mesmo do diagnóstico exato do evento.

Segundo a IAEA (2009), as funções críticas de segurança são definidas como necessárias para que a instalação previna ou mitigue consequências radiológicas em operação normal, antecipando assim ocorrências e condições de acidentes. Dentre as funções críticas de segurança de um reator nuclear podemos citar a manutenção da subcriticalidade do núcleo, após um evento, por exemplo, de desligamento do reator o resfriamento do núcleo e o inventário do nível de refrigerante do circuito primário e integridade do mesmo.

As funções críticas de segurança têm uma estrutura hierárquica de informações das variáveis que afetam a segurança da planta. Quando ocorre uma emergência na central nuclear, o operador deve monitorar periodicamente as FCS e identificar possíveis caminhos de sucesso para estabilizar ou desligar a planta usando procedimento operacional de emergência (POE). Os POEs incluem etapas para verificar as FCS. Esta verificação do estado das funções críticas de segurança é uma tarefa que provoca uma sobrecarga cognitiva que pode ser reduzida com a exibição de informações adequadas.

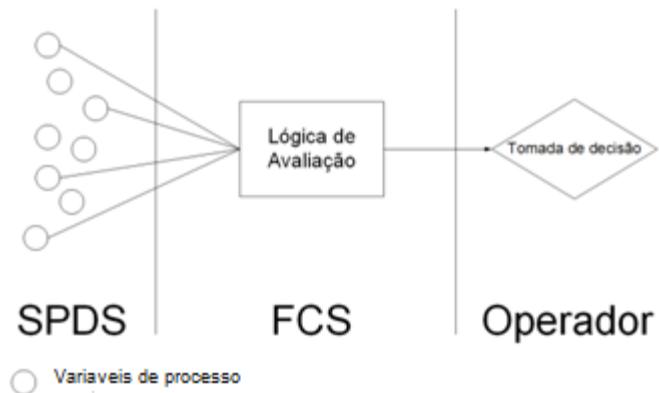

O Sistema de Monitoração de Parâmetros de Segurança (SPDS- *Safety Parameter Display System*) disponibiliza todas as variáveis necessárias para a atuação do sistema FCS.

O sistema de FCS tem a função de processar as variáveis que são importantes no processo através do Sistema de Monitoração de Parâmetros de Segurança (SPDS - *Safety Parameter Display System*).

A figura 6 apresenta a interação dos sistemas de SPDS e FCSe operador (NUREG, 1981).

Figura 6– Interação do sistema de SPDS e FCS e operador

A principal função do SPDS é servir como auxílio ao operador na rápida detecção de condições anormais, proporcionando uma visualização dos parâmetros da planta a partir da qual o estado de segurança da operação possa ser avaliado pelos operadores da sala de controle.

A monitoração das FCS torna possível ao operador detectar rapidamente as condições das funções críticas de segurança da planta e facilitar a tomada de decisão dos operadores.

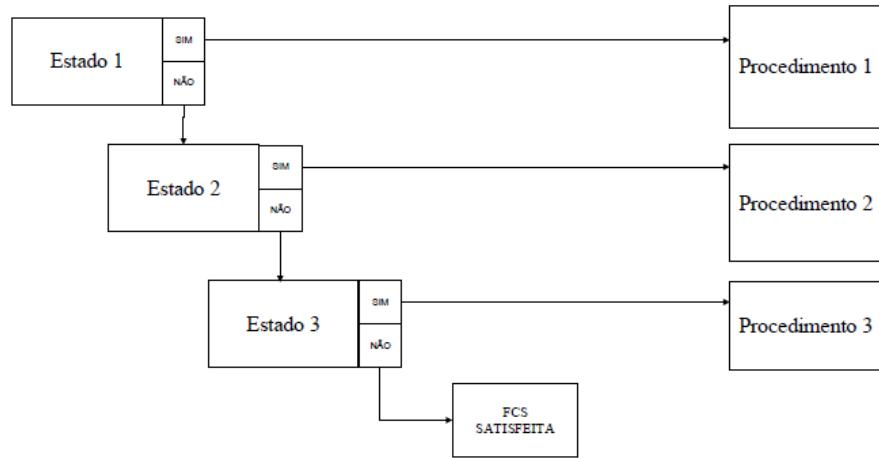

O direcionamento para a determinação do status de segurança da usina, independentemente da sequência de acidente ocorrida, está contido nas árvores de estados

das funções críticas de segurança. Existe uma árvore de estado para cada uma das funções críticas, sendo que o conjunto dessas árvores determina o estado de segurança da usina.

Um conjunto limitado de parâmetros deve ser avaliado de uma maneira sistemática para se determinar o estado de cada função. Uma estrutura ramificada do tipo “árvore de decisão/estado” é o veículo lógico para se estruturar a avaliação sistemática dos parâmetros da central que determinam o estado de cada função.

Árvore de estado é uma ferramenta utilizada para análise de confiabilidade de sistemas de proteção. Cada árvore de estado tem um único ponto de entrada e vários pontos de saída (ramos terminais) mutuamente exclusivos dependendo dos valores dos parâmetros especificados na árvore. Dessa forma, cada passada através de uma árvore de estado produz um único ponto de saída, ou seja, um único estado da função correspondente.

Uma árvore de estado representa um sistema, ou subsistema, por meio de um diagrama que possui um evento de topo, que ocorre a partir de uma combinação de outros eventos. Essa combinação é representada por símbolos que interligam esses eventos por meio de elementos lógicos, tais como “AND”, “OR”, etc.

Uma análise qualitativa pode ser feita a partir da verificação, na árvore de falhas, de quais eventos básicos e caminhos levam à ocorrência do evento topo. Por outro lado, a análise quantitativa é aplicada quando se determina a probabilidade de o evento topo ocorrer em função das probabilidades de eventos básicos. O diagrama permite visualizar as sequências de falhas que deverão ocorrer para que aconteça o evento topo. Após a construção da árvore de estado, podem-se inserir as probabilidades que cada evento representado tem de ocorrer, possibilitando o cálculo da probabilidade de acontecer o evento. A figura 7 apresenta uma árvore de estado para uma FCS.

Figura 7—Árvore de estados genérica

No SFCS quatro condições de estado (ameaça extrema, ameaça severa, anormal e satisfeita) são definidas para permitir a priorização dos estados de cada função crítica. Cada ramo (terminal) de uma árvore é classificado dentro de uma das quatro condições mencionadas acima, um código de linhas coloridas e símbolos de terminação são usados como mecanismo para informar imediatamente ao operador que cada função crítica está sendo ameaçada e para indicar o grau de severidade da ameaça. Cada estado caracteriza o grau de ameaça à FCS:

- Estado 1 – ameaça extrema(condição alta);

- Estado 2 – ameaça severa(condição média);

- Estado 3 – condição anormal (condição baixa);

- Estado 4 – Condição normal, FCS satisfeita.

O estado 1 indica o maior grau de ameaça à FCS; o estado 2, indica uma ameaça intermediaria entre o estado 1 e o 3 ,o estado 3 é a primeira indicação de que a FCS está sendo violada, o estado 4,indica a condição de normalidade e não violação da FCS .

Com exceção dos ramos terminais da função satisfeita, a cada ramo terminal da árvore é associado um procedimento de operação de emergência especialmente

redigido para direcionar as ações do operador no sentido de restaurar a condição "satisfieta" da função crítica correspondente. Esses procedimentos especiais são denominados "procedimentos de restauração de funções".

Existe uma árvore de estado para cada uma das FCS, sendo que o conjunto dessas árvores determina o estado de segurança da usina. O sistema de FCS avalia continuamente as árvores de estado e fornece em tempo real ao operador, através de meios gráficos, o estado atualizado de todas as funções críticas de segurança.

O sistema de FCS indica a prioridade das ações que devem ser tomadas pelo operador. Para isso existe uma hierarquização das FCS e das ameaças, em cada FCS. A equipe de operação verifica o cumprimento das FCS da planta fazendo a leitura de parâmetros relativos a cada uma delas e, em caso de ameaça, executa os procedimentos necessários.

O conjunto de funções críticas de segurança implementados no SFCS é constituído pelas seguintes funções:

- Subcriticalidade

- Resfriamento do núcleo

- Remoção de calor

- Integridade do sistema de refrigerante do reator

- Ambiente da contenção

- Inventário do refrigerante do reator

- A finalidade da função de segurança "subcriticalidade" é fornecer uma indicação do desligamento do reator.

- A função "resfriamento do núcleo" indica se o núcleo está sendo resfriado adequadamente ou não.

- A remoção de calor está relacionada com a capacidade do sistema de remoção de calor do circuito primário para o secundário da planta.

- A função crítica de segurança “integridade do sistema de refrigerante do reator” verifica se a pressão no sistema de resfriamento do reator, medida no pressurizador, está dentro dos limites especificados com base na temperatura do líquido de resfriamento, bem como a taxa de variação da temperatura do líquido de resfriamento.

- A função crítica de segurança “ambiente da contenção” fornece uma avaliação de vazamento de radiação, vapor ou água do circuito primário e secundário para o ambiente da contenção.

- Finalmente, o inventário de refrigerante do reator, que por meio do monitoramento dos níveis de água de refrigeração no pressurizador e vaso do reator, fornece informações úteis para determinar se a quantidade de água presente no sistema primário é satisfatória e/ou se uma bolha de vapor está sendo formada no vaso do reator.

O SFCS percorre sequencialmente as seis árvores de estado e fornece ao operador o estado atualizado de todas as funções críticas em tempo real; A hierarquização das funções obedece à ordem que foi apresentada anteriormente, ou seja, “subcriticalidade” é a função hierarquicamente mais alta e “inventário do refrigerante do reator” é a mais baixa. Em TMI a última que foi violada

O uso pelos operadores das funções críticas de segurança permite uma avaliação do estado de segurança da planta através de monitoração das variáveis de estado que as caracterizam, a análise em tempo real quanto às suas tendências e proteção por meio de um painel que mostre ao operador o grau de ameaça a cada FCS. Nesses casos, o sistema de FCS é utilizado para auxiliar o operador a levar a planta a uma parada segura. Em um reator nuclear, a modificação das às FCS têm importante papel para auxiliar os operadores a manter as condições seguras da unidade após um evento de desligamento da usina.

### **3FIELD PROGRAMMABLE GATE ARRAY (ARRANJO DE PORTAS LÓGICAS PROGRAMÁVEL EM CAMPO)**

Este capítulo tem como objetivo apresentar o conceito de FPGA (*Field Programmable Gate Array*) que consiste em um circuito integrado que contém um grande número de unidades lógicas idênticas que podem ser configuradas de formas independentes após sua fabricação. A habilidade de atualizar suas funcionalidades e reconfigurar partes do projeto e o baixo custo não-recorrente de engenharia em relação a um projeto ASIC (*Application-Specific Integrated Circuit*) oferecem vantagens para muitas aplicações. Neste capítulo também será abordado o conceito da configuração da FPGA, que é geralmente especificada utilizando Linguagem de Descrição de Hardware (VHDL - *Hardware Description Language*).

#### **3.1 DISPOSITIVO FPGA**

O dispositivo lógico FPGA (*Field Programmable Gate Array*) é um circuito integrado que contém um grande número de unidades lógicas idênticas que podem ser configuradas de formas independentes e interconectadas a partir de uma matriz de trilhas condutoras e *switches* (chaves) programáveis. A partir do amadurecimento da tecnologia de FPGA, as primeiras arquiteturas reconfiguráveis foram criadas com o intuito principal de aumentar o desempenho de algoritmo que até então era executado em um software (Mesquita, 2002).

De acordo com Gonçalves (Gonçalves et al., 2003), esta tecnologia propicia chips extremamente eficientes e totalmente reaproveitáveis, pois estes podem ser reprogramados e reutilizados quantas vezes forem necessárias.

De acordo com Martin (Martin et al.,2003) uma arquitetura reconfigurável pode compartilhar todas as características de uma arquitetura tradicional.

### 3.2 USO DE FPGA EM SISTEMAS DE SEGURANÇA NUCLEAR

Devido aos efeitos do envelhecimento, os problemas de obsolescência, degradação ambiental e falhas mecânicas, as tecnologias de relé convencional e eletrônica analógica tornaram-se uma questão problemática para as usinas nucleares, que precisam substituir estes sistemas mais antigos por sistemas baseados em tecnologias digitais.

A utilização de tecnologias digitais baseadas em software para funções críticas e de segurança em usinas nucleares tem se mostrado problemática e custosa, principalmente em função dos requisitos para projeto de software exigidos pelas normas de projeto de software para funções críticas e de segurança, como por exemplo, a IEEE 880 (1995).

Conforme a IEEE 880(1995), quando um novo sistema com base digital é utilizado para substituir um sistema analógico, ele tem que ser desenvolvido de forma criteriosa e passar por um exame minucioso por órgãos reguladores para que possa ser autorizada sua operação na planta. Este processo de aprovação pode ser muito custoso e demorado devido à complexidade envolvida na certificação para o desenvolvimento de lógicas baseadas em software.

O projeto de um sistema em FPGA é feito através de um fluxo de projeto de sistema digital padrão, que pode ser implementado em FPGA de diferente hardware. Em outras palavras, o projeto (especificações do sistema, fluxograma lógico, código fonte, e simulação funcional) é independente do software específico e as plataformas de hardware em que está implementado, tornando o sistema FPGA "círcuito independente". Mesmo se um Chip de FPGA não estiver mais disponível no futuro, o projeto será certificado e ainda será válido. O projeto pode ser implementado em um

chip FPGA e todas as funcionalidades projetadas permanecem inalteradas. Estas características tornam a tecnologia FPGA uma nova opção para o projeto de sistemas de segurança de usinas nucleares.

O FPGA tem muitas vantagens, pois é essencialmente livre do sistema operacional, fornece de forma independente sinais paralelos semelhantes aos circuitos analógicos convencionais. O número de modos de falha de um sistema utilizando FPGA é muito menor do que um que opera sobre um sistema operacional.

O processo de aprovação pode ser significativamente simplificado. Vários projetos bem-sucedidos têm sido realizados em todo o mundo (Clarkson, 2008; Nakagawa, 2008; Nguyen, 2008). Um exemplo interessante é documentado por Clarkson (2008) mostrando que US NRC levou apenas dois anos para concluir o processo de certificação, que é muito mais curto do que um baseado em software, que pode durar mais de 10 anos.

Outra vantagem de implementação do FPGA é o aumento da velocidade das lógicas de processamento. Esta capacidade de processamento de alta velocidade pode trazer benefícios adicionais para a segurança de uma usina nuclear. A função mais importante de qualquer sistema de segurança I & C em uma usina nuclear é parar a reação em cadeia e absorver nêutrons em um evento de um acidente.

Um sistema de desligamento mais rápido seria muito importante para segurança das instalações.

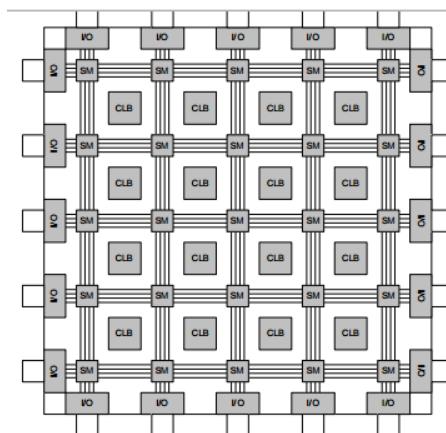

### 3.3 AS ESTRUTURAS DE UM FPGA

Um FPGA possui três elementos básicos que podem ser definidos como: bloco de lógica configurável (CLB - *Configurable Logic Block*), as interconexões, e os blocos de entrada/saída (I/O - *Input/Output*). A estrutura fornece acesso individual selecionável de entrada, saída ou bidirecional, ao mundo externo. A matriz distribuída de interconexões programáveis fornece interconexões aos CLBs e conexões aos

blocos de I/O. FPGAs grandes podem ter dezenas de milhares de CLBs, além de memória e outros recursos.

A maioria dos fabricantes de dispositivos de lógica programável produz uma série de FPGAs que variam em densidade, consumo de energia, tensão de alimentação, velocidade, e até certo ponto variam em arquitetura. FPGAs são reprogramáveis e usam as tecnologias SRAM (volátil) ou antifuse (não-volátil) para programar as interconexões.

### 3.3.1 Definição de blocos lógicos

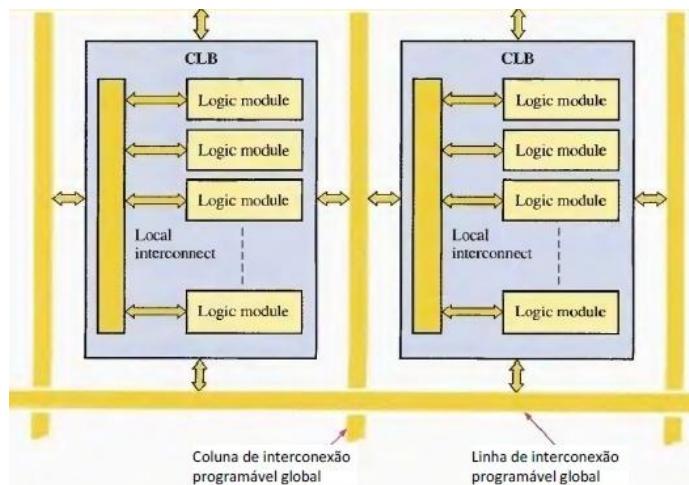

As funções lógicas são implementadas no interior dos Blocos Lógicos. Esses blocos lógicos programáveis (CLB – *Configurable Logic Block*) são distribuídos pelo integrado no meio de uma matriz de interligações que estabelecem ligações entre blocos lógicos e entre um bloco lógico e um de I/O. Os blocos de I/O estão colocados em torno do integrado como visto na figura 8:

Figura 8—Arquitetura genérica de uma FPGA

Os CLB (Bloco Lógico Configurável) encontram-se dispostos ao longo do integrado numa estrutura regular. No cruzamento das ligações horizontais e das verticais, existe um módulo configurável designado matriz de ligação (SM) em que se programam as interligações. O número de CLB, de SM e de blocos de I/O, bem como a estrutura interna de cada um destes blocos, varia com o fabricante e depende da família e do tipo de FPGA.

A Figura 9 mostra um CLB dentro das linhas/colunas de interconexões programáveis globais que são utilizadas para conectar os CLBs. Cada CLB é constituído por múltiplos módulos lógicos menores e uma interconexão programável local que é utilizada para conectar os módulos lógicos dentro do CLB.

Figura 9—Configuração básica de um CLB

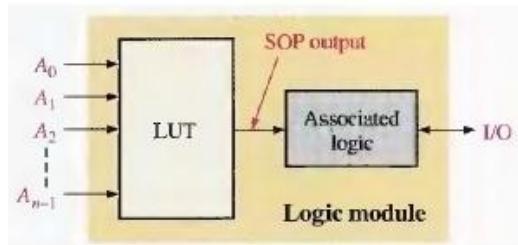

Quando um circuito lógico é sintetizado em um FPGA, os blocos lógicos são programados para realizar as funções necessárias, e os canais de roteamento são estruturados de forma a realizar a interconexão necessária entre os blocos lógicos. As células de armazenamento de memória são voláteis, o que implica na perda do conteúdo armazenado, no caso de falta de suprimento de energia elétrica. Dessa forma, o FPGA deve ser programado toda vez que for energizado. Um módulo lógico em um CLB pode ser configurado para lógica combinacional, lógica de registrador ou uma combinação de ambos. Um flip-flop é parte da lógica associada e é utilizado

para a lógica de registrador. O diagrama de blocos da Figura 10 mostra os componentes de um módulo lógico.

Figura 10– Diagrama de bloco de um módulo lógico.

O LUT (*Look-Up Table*) é um tipo de memória programável utilizada para gerar soma de produtos.

Geralmente utiliza-se uma pequena memória Flash ou EEPROM (*Electrically Erasable Programmable Read Only Memory*), cuja função é carregar automaticamente as células de armazenamento. Toda vez que o FPGA for energizado, esta flexibilidade de programação, associada a potentes ferramentas de desenvolvimentos e modelagem, possibilita ao usuário acesso a projetos de circuitos integrados complexos sem os altos custos de engenharia, necessários no uso de Asics (*Application Specific Integrated Circuits*). ASICS são circuitos integrados que precisam de um processo de fabricação especial, que requer máscaras específicas para cada projeto. Outra característica dos circuitos integrados ASICs é o tempo de desenvolvimento longo e os custos extremamente altos. Geralmente não necessitam de muitos componentes externos para a realização de uma função específica, pois sua alta densidade os torna aptos para a implementação de vários tipos de aplicação.

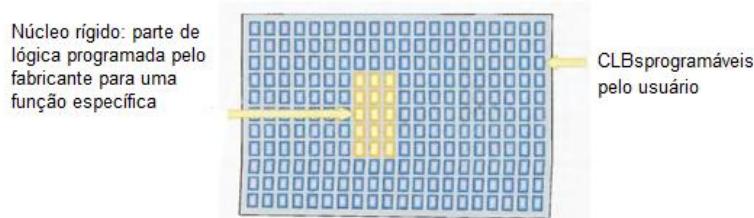

### 3.3.2 Núcleo de FPGA

Existem dois tipos de núcleos de FPGA: núcleo rígido e núcleo flexível. Um núcleo rígido é uma parte de lógica em uma FPGA que é colocada pelo fabricante para fornecer uma função específica, e não pode ser reprogramada. Uma vantagem na utilização de núcleos rígidos é que um projeto implementado em um FPGA utilizando um núcleo rígido ocupa menos espaço no FPGA do que o mesmo projeto implementado em campo por um usuário, resultando em uma economia de elementos lógicos e menor tempo de desenvolvimento. Além disto, as funções do núcleo rígido já foram exaustivamente testadas. A desvantagem dos núcleos rígidos é que as especificações são fixadas durante o processo de fabricação, e o consumidor não poderá alterar a lógica.

Núcleos rígidos são geralmente disponíveis para funções que são usualmente utilizadas como microprocessadores, interface padrão de I/O, e processadores digitais de sinais. Mais de um núcleo rígido pode ser programado em uma FPGA. A Figura 11 ilustra o conceito de um núcleo rígido rodeado por elementos lógicos programáveis pelo usuário.

Figura 11—Modelo de um núcleo rígido embutido em uma FPGA

Núcleos rígidos são geralmente desenvolvidos pelos fabricantes de FPGA. Projetos de propriedade do fabricante são denominados de IP (*Intellectual Property*). A empresa geralmente relaciona em seu site os tipos de IP que estão disponíveis. Um

núcleo flexível é uma parte de lógica que é programada pelo usuário e pode ser modificada.

Projetos de núcleos flexíveis podem ser encontrados prontos ou podem ser desenvolvidos. As desvantagens na sua utilização são a maior utilização da capacidade da FPGA e o maior tempo de desenvolvimento para o usuário, pois mesmo que o projeto esteja pronto, pode ser necessária a realização de testes e modificações. A sua vantagem está na sua flexibilidade de poder ser modificado.

### **3.3.3 Desenvolvimento de projetos em FPGA**

Ao longo dos últimos anos, o uso de FPGAs tem aumentado muito nos produtos comerciais e militares. Eles podem ser encontrados em radares, na comunicação via satélite, produção, indústria automotiva, e muitos outros tipos de produtos. Independente do produto final, projetistas de FPGA seguem um mesmo processo básico.

Os estágios de desenvolvimento em FPGA são design, captura de esquemático, simulação, síntese e implementação.

- Design: O processo de design envolve a conversão dos requisitos para um formato que representa a função digital desejada. Os formatos de concepção mais comuns são a captura de esquemático e a linguagem de descrição de hardware (HDL), ou uma combinação dos dois. Embora cada método tenha suas vantagens e desvantagens, HDLs geralmente oferecem grande flexibilidade de design.

- Captura de esquemático: A captura de esquemático é uma representação gráfica de um projeto digital, onde mostra a interligação efetiva entre as portas lógicas que produzem as funções de saída desejadas. Muitas destas funções envolvem informações proprietárias, e são fornecidas ao projetista apenas

através da biblioteca do fornecedor específico da FPGA. A natureza exclusiva deste tipo de projeto faz com que seja dependente do fornecedor, e o processo de design inteiro deve ser repetido se um fornecedor diferente é usado. Exemplos de ferramentas de captura de esquemáticos são *Viewlogic's ViewDraw* e *HDL's EASE*. A principal vantagem da utilização da captura de esquemático é que a representação gráfica é de fácil compreensão. No entanto, sua maior desvantagem é um aumento no custo e tempo para reproduzir um projeto para diferentes fornecedores, devido à natureza proprietária do desenho.

- Simulação: A simulação é o ato de verificar o design antes da validação do hardware real. As características dos sinais de entrada do circuito são descritos em HDL ou graficamente, e então aplicados ao design. Isso permite que o responsável pela verificação do código possa observar o comportamento das saídas.

- Síntese: O primeiro passo no processo de síntese é compilar o design em elementos estruturais. A etapa seguinte envolve a otimização do design, tornando-o menor e mais rápido, removendo lógicas desnecessárias e permitindo que os sinais cheguem às entradas ou saídas mais rapidamente. O passo final no processo de síntese envolve o mapeamento ou associação do design à arquitetura específica de um fornecedor. O processo de mapeamento define as conexões do design na FPGA, usando a arquitetura do fabricante específico.

- Implementação: A última fase no processo de desenvolvimento de projeto em FPGA é a implementação, também conhecida como PAR (*Place And Route*). O primeiro passo no processo de implementação é chamado tradução. A tradução envolve a verificação da coerência entre a síntese do design e a FPGA alvo. Alguns exemplos de incoerência são: dois sinais diferentes serem atribuídos ao mesmo pino, atribuição de um sinal ao pino Vcc ou terra ou atribuir um sinal a um pino não existente. O segundo passo é a distribuição da

lógica do design na FPGA. O último passo é gerar o arquivo de programação que pode ser gravado em uma memória flash, PROM ou diretamente na FPGA, dependendo do fabricante.

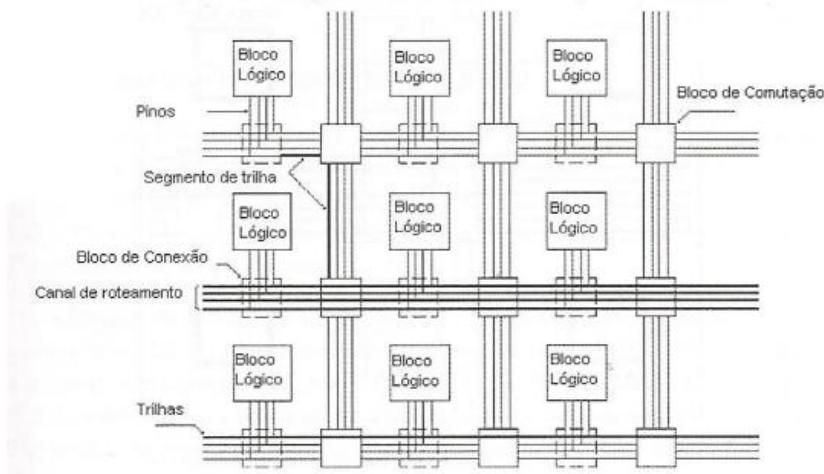

### 3.3.4 Arquitetura geral de roteamento

A arquitetura de roteamento de um FPGA é a forma pela qual os seus barramentos e as chaves de comutação são posicionados para permitir a interconexão entre as células lógicas. Essa arquitetura deve permitir que se obtenha um roteamento completo e ao mesmo tempo, alta densidade de portas lógicas. Para melhorar a compreensão dessa arquitetura é necessária a definição de alguns conceitos básicos, sendo que parte deles é exemplificada na figura 12.

Figura 12—Arquitetura básica de roteamento de um FPGA

- Pinos: Entrada e Saída de blocos lógicos.

- Conexão: Ligação elétrica de um par de pinos

- Rede: Conjunto de pinos que estão conectados.

- Bloco de Comutação: Utilizado para conectar os segmentos da trilha.

- Segmentos da Trilha: Segmento não interrompido por chaves programáveis.

- Canal de Roteamento: Grupo de 2 ou mais 3 trilhas paralelas.

- Bloco de Conexão: Permite a conectividade das entradas e saídas de

- Um bloco lógico com os segmentos de trilhas nos canais.

### 3.4 FPGAS COMERCIAIS

Primeiro vieram PROMs e PLDs, matrizes de portas reconfiguráveis. Algumas patentes de equipamentos parecidos com FPGAs surgiram no final dos anos 80 e início dos anos 90 (Casselman, Page, Peterson) Os fundadores da Xilinx, Ross Freeman e Bernard Vonderschmitt, inventaram o primeiro FPGA comercial em 1985 – o XC2064.

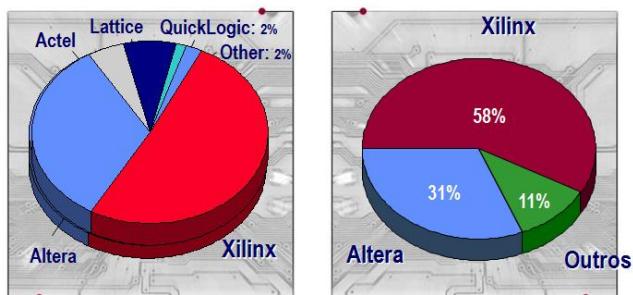

Há vários fabricantes de FPGA, destacando-se a Altera e a Xilinx. Qualquer um destes fabricantes já possui FPGA com capacidades de integração que podem ir até cerca de 10 milhões de portas equivalentes, incluindo blocos integrados dedicados. A figura 13 mostra o mercado de FPGA no ano de 2005.

Figura 13—Mercado de FPGA no ano de 2005

Fonte:Xilinx Company reports

### 3.5 FPGA NA INDÚSTRIA

FPGA é utilizado em diversos setores da indústria, está presente em setores onde desempenho, paralelismo e tempo real são cruciais. Por se tratar de hardware, é possível realizar uma instrução por ciclo de *clock*, podemos ter vários cálculos rodando em paralelo e entregando o resultado no mesmo pulso de *clock* - algo completamente impossível para um software realizar. Basicamente sempre que alto processamento, paralelismo e tempo real forem necessários, a utilização de um FPGA deve ser considerada.

Para citar alguns mercados em que FPGA é forte:

- Setor elétrico, para processamento digital de sinal em tempo real;

- Setor de telecomunicação, em switches e roteadores de alto desempenho;

- Setor de multimídia, para processamento de imagens em tempo real e alto desempenho;

- Setor militar, dentre outros.

### 3.6 LINGUAGEM DE DESCRIÇÃO DE HARDWARE (VHDL)

Uma linguagem de descrição de circuito padronizada possibilita o intercâmbio de informações referentes ao comportamento de um circuito entre fabricantes, fornecedores de sistemas e empresas de projetos.

O *Hardware Description Language* (VHDL) é uma notação formal para uso em todas as fases de criação de sistemas eletrônicos, suporta o desenvolvimento, verificação, síntese e análise de projetos de hardware; a comunicação de hardware e dados de projeto; e a manutenção, modificação, e aquisição de hardware adaptado da norma (IEEE Std 1076, 2000).

VHDLé uma forma de se descrever, através de um programa, o comportamento de um circuito ou componente digital que será executado por um (simulador) software. Um sistema descrito em linguagem de *hardware* pode ser implementado em um dispositivo programável, permitindo assim o uso em campo do seu sistema, tendo a grande vantagem da alteração do código a qualquer momento.

### 3.6.1 Níveis de abstração e descrição

A linguagem VHDL permite dividir o sistema em diferentes níveis de abstração: nível de sistema, nível de transferência entre registradores (*RT level*), nível lógico e nível de circuito. Permite três diferentes domínios de descrição: comportamental, estrutural e físico.

- Nível de sistema:

descrição comportamental: *algoritmos*

descrição estrutural: *processadores e memórias*

descrição física: *boards e chips*

- Nível RT:

Descrição comportamental: *transferências entre registradores*

Descrição estrutural: *registradores, unidades funcionais*

Descrição física: *chips e módulos*

- Nível Lógico:

Descrição comportamental: *equações booleanas*

Descrição estrutural: *gates e flip-flops*

Descrição física: *módulos e células*

- Nível de Circuito:

Descrição comportamental: *funções de transferência*

Descrição estrutural: *transistores e conexões*

Descrição física: *células e segmentos do circuito*

### 3.6.2 Componentes do VHDL

É fundamental, para todo e qualquer sistema, uma interface com o mundo externo. Em VHDL esta interface é chamada *entidade*. Para se atingir a funcionalidade desejada, os dados devem sofrer transformações dentro do sistema. Esta parte interna do sistema responsável pelas transformações dos dados é chamada de corpo ou arquitetura. Para definir quais implementações serão utilizadas no projeto, usamos o recurso da configuração. Alguns sistemas necessitam de funcionalidades adicionais, que são conhecidas como *biblioteca*.

Segundo a norma IEEE (IEEE Std 1076, 2000), a entidade do projeto é a abstração de hardware primário em VHDL. Ela representa uma parte de um desenho de hardware que possui entradas e saídas bem definidas e executa uma função bem definida. A entidade pode representar todo um sistema, um subsistema, uma placa, um chip, uma célula macro, uma porta lógica, ou qualquer nível de abstração entre eles. A configuração pode ser usada para descrever a forma como as entidades são colocadas juntas para formar um projeto. A norma também diz que uma entidade de criação pode também ser descrita em termos de componentes interligados. Cada componente de um projeto (entidade) pode ser ligada a uma entidade de nível mais baixo de criação, de modo a definir a estrutura ou funcionamento desse componente.

A Decomposição sucessiva de uma entidade em componentes e os componentes de ligação em outras entidades de design que podem ser decompostas de igual modo resultam em uma hierarquia de entidades representando um projeto completo. Essa coleção de entidades de projeto é chamada de *hierarquia de hardware*. As ligações necessárias para identificar uma hierarquia do hardware podem ser especificadas em uma configuração da entidade de nível superior na hierarquia. Esta disposição

descreve a maneira pela qual as entidades e configurações são definidas. A entidade é definida por uma declaração de entidade, em conjunto com um corpo (arquitetura) correspondente.

## 4FPGA NAS FUNÇÕES CRÍTICAS DE SEGURANÇA NO LABIHS

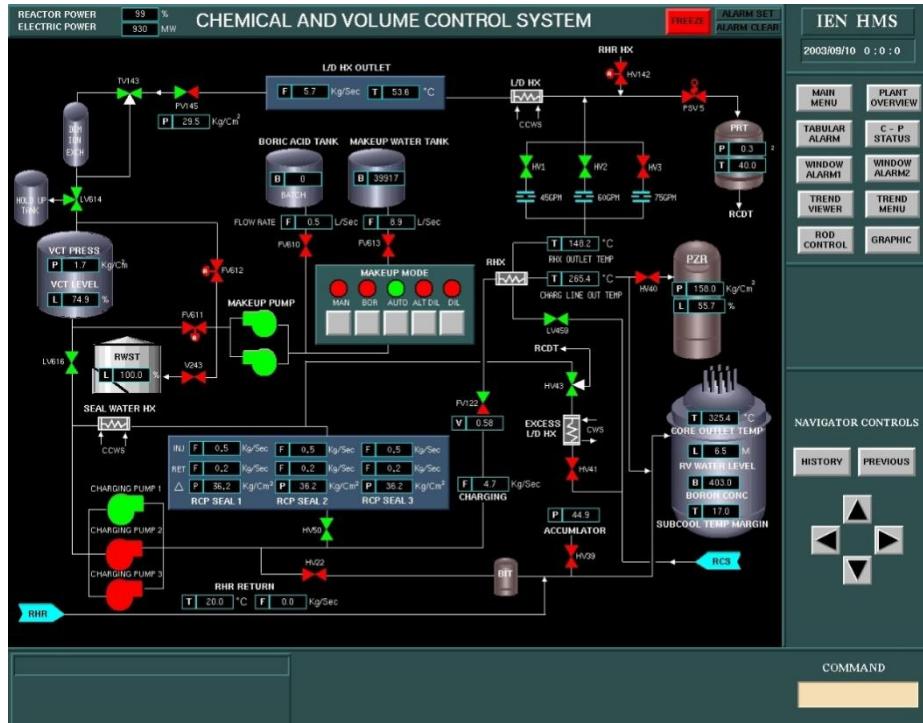

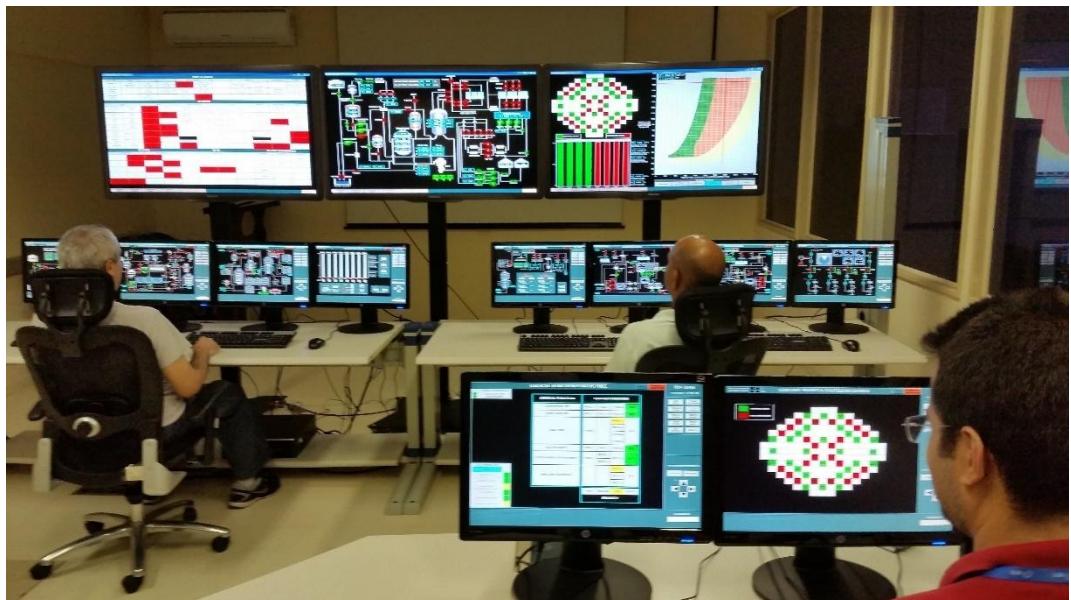

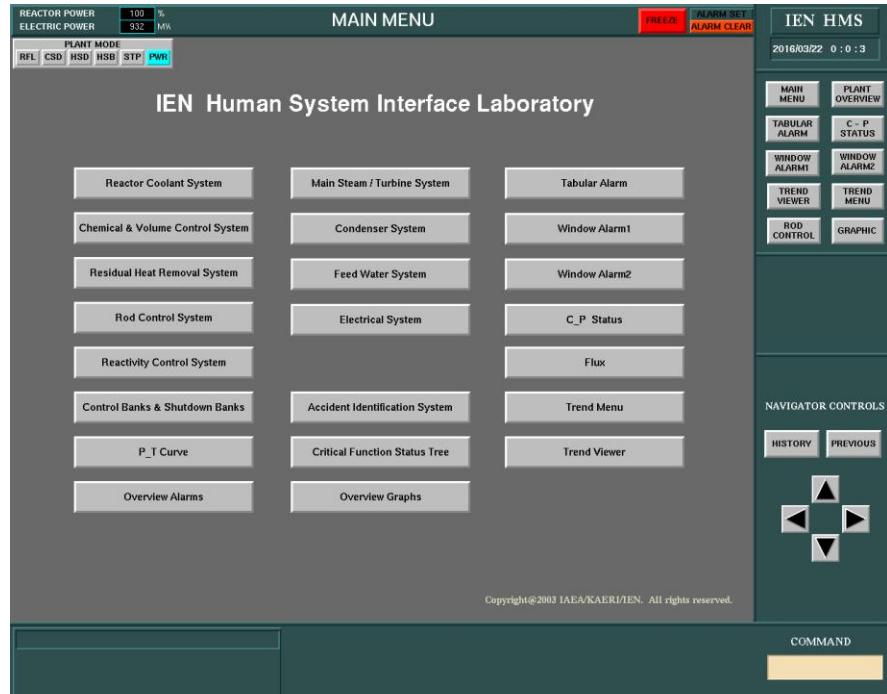

Este capítulo tem como objetivo apresentar o funcionamento do simulador do Laboratório de Interfaces Homem-Sistema (LABIHS) mais especificamente sobre a Interface das Funções Críticas de Segurança, e apresentar o funcionamento do Quartus que dispõe de mecanismos para compilar o projeto. Para um melhor entendimento deste capítulo também são abordados os conceitos de sala de controle digital de um reator nuclear e a sala de controle digital do simulador do LABIHS.

### 4.1 SALAS DE CONTROLE DIGITAL

Uma sala de controle contém os sistemas e as informações necessárias para o controle das condições operacionais de uma planta industrial, de modo a assegurar o seu funcionamento e desligamento confiável e seguro, em situações normais e de acidentes (ISO 11064, 2002).

As salas de controle digital de reatores nucleares são constituídas por um arranjo de sistemas e equipamentos, onde os operadores monitoram, controlam e intervêm no processo. Os operadores realizam na sala de controle procedimentos relativos à partida e parada do reator nuclear, emergência, sistema de alarmes, sistema de comunicação, sistema de controle, sistema de segurança e verificam diagnóstico de falhas. Os sistemas são informatizados, com grande redundância e interconectividade, além do alto grau de confiabilidade através de várias interfaces gráficas e estações de monitoramento. Essas estações precisam estar dispostas de modo que auxiliem os operadores em seus manuseios, tanto para operações rotineiras quanto para prevenções de acidentes.

#### 4.1.1 Sala de controle do simulador LABIHS

O simulador do Laboratório de Interfaces Homem-Sistema (LABIHS) localizado na Divisão de Engenharia Nuclear (DENN) do Instituto de Engenharia Nuclear, IEN/CNEN, foi desenvolvido em conjunto com o *Korean Atomic Energy Research Institute* (KAERI). É um simulador compacto de um reator nuclear do tipo PWR (*Pressurized water reactor*), baseado nas plantas de referência Kori 3&4. A sala de controle consiste de uma rede de computadores tipo PC, que funcionam como terminais de uma estação de trabalho HP 3700, na qual opera o simulador compacto.